| 번호 | 청구항 |

|---|---|

| 2 | 제1항에 있어서,상기 비휘발성 메모리 셀이 커패시터(capacitor)를 포함하지 않는 캡리스 비휘발성 메모리 셀인 것을 특징으로 하는 비휘발성 메모리 셀. |

| 3 | 제1항에 있어서,상기 비정질 p형 반도체가셀레늄 원자(Se) 및 황 원자(S)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 칼코겐 원자; 및 텔루륨(Te) 원자 및 텔루륨 옥사이드를 포함하는 텔루륨 복합체;를 포함하는 것을 특징으로 하는 비휘발성 메모리 셀. |

| 4 | 제3항에 있어서,상기 칼코겐 원자가 상기 텔루륨 복합체와 합금된(alloyed) 것을 특징으로 하는 비휘발성 메모리 셀. |

| 5 | 제3항에 있어서,상기 비정질 p형 반도체가 아래 화학식 1로 표시되는 것을 특징으로 하는 비휘발성 메모리 셀.[화학식 1] TeOx:M상기 화학식 1에서, M은 황 원자(S) 또는 셀레늄 원자(Se)이고, x는 0003c#x003c#2이다. |

| 6 | 제3항에 있어서,상기 비정질 p형 반도체의 텔루륨 원자가 Te4+의 이온화 상태, Te2+ 의 이온화 상태 및 Te0의 비이온화 상태를 포함하는 것을 특징으로 하는 비휘발성 메모리 셀. |

| 7 | 제3항에 있어서,상기 텔루륨 옥사이드가 일산화 텔루륨(TeO) 및 이산화 텔루륨(TeO2)를 포함하는 것을 특징으로 하는 비휘발성 메모리 셀. |

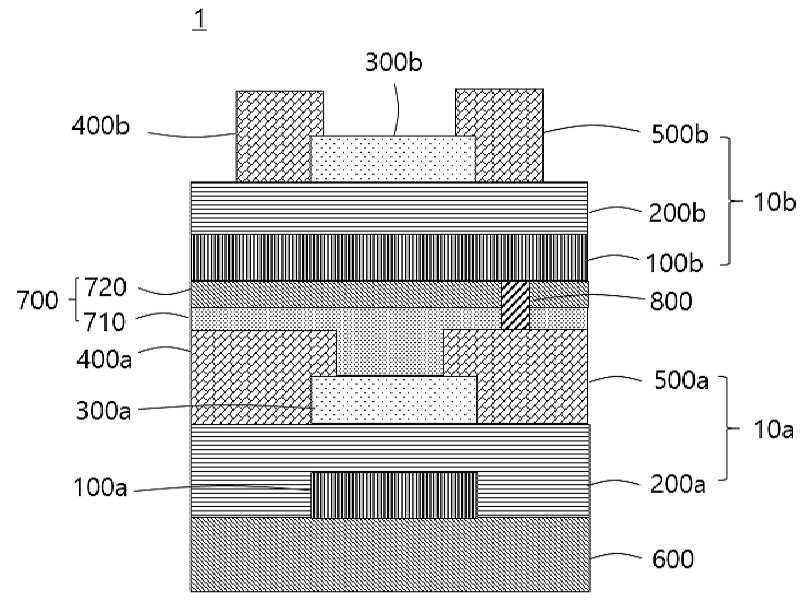

| 1 | 제1 반도체층을 포함하는 쓰기 n형 트랜지스터 및 제2 반도체층을 포함하는 읽기 p형 트랜지스터를 포함하고,상기 제1 반도체층은 n형 반도체를 포함하고,상기 제2 반도체층은 비정질 p형 반도체를 포함하는 것인,비휘발성 메모리 셀. |

| 8 | 제3항에 있어서,상기 비정질 p형 반도체가 산소 결핍 상태인 것을 특징으로 하는 비휘발성 메모리 셀. |

| 9 | 제1항에 있어서,상기 비휘발성 메모리 셀은 상기 쓰기 n형 트랜지스터(10a)와 상기 읽기 p형 트랜지스터가 교대로 수직 적층된 것을 특징으로 하는 비휘발성 메모리 셀. |

| 10 | 제9항에 있어서,상기 쓰기 n형 트랜지스터와 상기 읽기 p형 트랜지스터가 수직 적층된 것이 수직 방향으로 복수회 반복하여 적층된 것을 특징으로 하는 비휘발성 메모리 셀. |

| 11 | 제9항에 있어서,상기 쓰기 n형 트랜지스터가 제1 게이트 전극과, 상기 제1 게이트 전극 상에 위치하는 제1 절연층과, 상기 제1 절연층 상에 위치하는 제1 반도체층과, 제1 소스 전극 및 제1 드레인 전극을 포함하고,상기 읽기 p형 트랜지스터가 제2 게이트 전극과, 상기 제2 게이트 전극 상에 위치하는 제2 절연층과, 상기 제2 절연층 상에 위치하는 제2 반도체층과, 제2 소스 전극 및 제2 드레인 전극을 포함하고,상기 쓰기 n형 트랜지스터와 상기 읽기 p형 트랜지스터 사이에 절연성 중간층이 위치하는 것을 특징으로 하는 비휘발성 메모리 셀. |

| 12 | 제11항에 있어서,상기 절연성 중간층이 SU-8, CYTOP, Benzocyclobutene(BCB) 및 polyimide로 이루어진 군으로부터 선택된 1종 이상을 포함하는 제1 절연성 중간층; 및 상기 제1 절연성 중간층 상에 위치하고, Al2O3, HfO2, Al2O3와 HfO2의 적층체(Al2O3/HfO2), CYTOP, BCB 및 polyimide로 이루어진 군으로부터 선택된 1종 이상을 포함하는 제2 절연성 중간층; 을 포함하는 것을 특징으로 하는 비휘발성 메모리 셀. |

| 13 | 제11항에 있어서,상기 비휘발성 메모리 셀이 상기 쓰기 n형 트랜지스터의 제1 드레인 전극과 상기 읽기 p형 트랜지스터의 제2 게이트 전극을 전기적으로 연결하는 비아(via)을 추가로 포함하는 것을 특징으로 하는 비휘발성 메모리 셀. |

| 14 | 제1항에 있어서,상기 n형 반도체가 MoS2, ZnO, In2O3, TiO2, Ga2O3, VO2, V4O9, VOx,indium tin oxide(ITO), indium zinc oxide (IZO), indium zinc tin oxide (IZTO), indium gallium zinc oxide (IGZO), indium tungsten oxide(IWO) 및 zinc tin oxide (ZTO)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 것을 특징으로 하는 비휘발성 메모리 셀. |

| 15 | 제1항에 있어서,상기 비휘발성 메모리 셀이상기 쓰기 n형 트랜지스터의 제1 게이트 전극에 접속되는 쓰기 워드라인(WWL); 상기 쓰기 n형 트랜지스터의 제1 소스 전극에 접속되는 쓰기 비트라인(WBL); 상기 읽기 p형 트랜지스터의 제2 소스 전극에 접속되는 읽기 비트라인(RBL); 및 상기 읽기 p형 트랜지스터의 제2 드레인 전극에 접속되는 읽기 워드라인(RWL);을 추가로 포함하고,상기 쓰기 n형 트랜지스터의 제1 드레인 전극은 상기 읽기 p형 트랜지스터의 제2 게이트 전극에 접속되는 것을 특징으로 하는 비휘발성 메모리 셀. |

| 16 | (a) 제1 반도체층을 포함하는 쓰기 n형 트랜지스터 및 제2 반도체층을 포함하는 읽기 p형 트랜지스터로 이루어진 군으로부터 선택된 어느 하나의 트랜지스터를 제조하는 단계; 및(b) 제1 반도체층을 포함하는 쓰기 n형 트랜지스터 및 제2 반도체층을 포함하는 읽기 p형 트랜지스터로 이루어진 군으로부터 선택된 다른 하나의 트랜지스터를 상기 단계(a)에서 제조된 상기 트랜지스터 상에 수직으로 적층하여 제조하는 단계;를 포함하고,상기 제1 반도체층은 n형 반도체를 포함하고, 상기 제2 반도체층은 비정질 p형 반도체를 포함하는 것인, 비휘발성 메모리 셀의 제조방법. |

| 17 | 제16항에 있어서,상기 비휘발성 메모리 셀의 제조방법이 상기 단계(a)와 상기 단계(b) 사이에,(a') 상기 단계(a)에서 제조된 트랜지스터 상에 절연성 중간층을 형성하는 단계;를 추가로 포함하는 것을 특징으로 하는 비휘발성 메모리 셀의 제조방법. |

| 18 | 제16항에 있어서,상기 단계(a) 및 상기 단계(b)에서, 상기 비휘발성 메모리 셀의 기판의 온도가 5 내지 50 ℃인 것을 특징으로 하는 비휘발성 메모리 셀의 제조방법. |

| 19 | 제16항에 있어서,상기 단계(a) 또는 상기 단계(b)에서, 상기 제1 반도체층이 150 내지 400 ℃의 온도 범위에서 어닐링(annealing)되는 것을 특징으로 하는 비휘발성 메모리 셀의 제조방법. |

| 20 | 제16항에 있어서,상기 단계(a) 또는 상기 단계(b)에서, 상기 제2 반도체층이 150 내지 400 ℃의 온도 범위에서 어닐링(annealing)되는 것을 특징으로 하는 비휘발성 메모리 셀의 제조방법. |