| 번호 | 청구항 |

|---|---|

| 1 | 소수성 2차원 물질(hydrophobic 2-dimensional material)을 포함하는 소수성층(hydrophobic layer); 및상기 소수성층 상에 형성되고, 주석계 페로브스카이트를 포함하는 반도체층(semiconductor layer);을포함하는 주석계 페로브스카이트 적층체. |

| 2 | 제1항에 있어서,상기 소수성 2차원 물질이 헥사고날 보론나이트라이드(hexagonal boron nitride, hBN), 그래핀(graphene) 및 2차원 전이금속 디칼코겐 화합물((2D transition metal dichalcogenide, 2D TMD))로 이루어진 군으로부터 선택된 1종 이상을 포함하는 것을 특징으로 하는 주석계 페로브스카이트 적층체. |

| 3 | 제2항에 있어서,상기 2차원 전이금속 디칼코겐이 아래 화학식 1로 표시되는 화합물을 포함하는 것을 특징으로 하는 주석계 페로브스카이트 적층체:[화학식 1]MX2상기 화학식 1에서,M은 Mo, W, V, Nb, Ta, 또는 Ti이고,X는 S, Se, Te 또는 Po이다. |

| 4 | 제1항에 있어서,상기 2차원 전이금속 디칼코겐이 이황화텅스텐(WS2), 이황화몰리브덴(MoS2), 이셀레늄화텅스텐(WSe2) 및 이셀레늄화몰리브덴(MoSe2)으로 이루어진 군으로부터 선택된 1종 이상을 포함하는 것을 특징으로 주석계 페로브스카이트 적층체. |

| 5 | 제1항에 있어서,상기 소수성층의 수접촉각이 85 내지 110˚의 범위인 것을 특징으로 하는 주석계 페로브스카이트 적층체. |

| 6 | 제1항에 있어서,상기 주석계 페로브스카이트가 아래 구조식 1로 표시되는 화합물을 포함하는 것을 특징으로 하는 주석계 페로브스카이트 적층체.[구조식 1] Aa(B(1-b)Cb)cSnd(X(1-e)Ye)f상기 구조식 1에서,A는 세슘(Cs)이고,B 및 C는 서로 다르고, 각각 독립적으로 메틸암모늄(MA) 또는 포름아미디늄(FA)이고,a는 0≤a≤1의 실수이고, b는 0≤b≤1의 실수이고,c는 0≤c≤1의 실수이고, a 및 c는 동시에 0은 아니고, d는 0.5≤d≤1의 실수이고,X 및 Y는 서로 다르고, 각각 독립적으로 불소(F), 염소(Cl), 브롬(Br) 또는 요오드(I)이고,e는 0≤e≤1의 실수이고,f는 2.5≤f≤3.5의 실수이다. |

| 7 | 제4항에 있어서,상기 주석계 페로브스카이트가 CsI로 도핑된 것을 특징으로 하는 주석계 페로브스카이트 적층체. |

| 8 | 제4항에 있어서,상기 주석계 페로브스카이트가 cesium tin triiodide (CsSnI3), methylammonium tin triiodide(MASnI3), formamidinium tin triiodide(FASnI3) 및 Cesium formamidinium tin triiodide(CsFASnI3)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 것을 특징으로 주석계 페로브스카이트 적층체. |

| 9 | 제1항에 있어서,상기 반도체층이 첨가제를 추가로 포함하고,상기 첨가제가 상기 반도체층을 기준으로 0.1 내지 50 mol%로 첨가되는 주석계 페로브스카이트 적층체. |

| 10 | 제9항에 있어서,상기 첨가제가 PbCl2, SnCl2, CsCl, FACl(formamidinium chloride), MACl(methylammonium chloride)), PbAc2(lead(II) acetate), SnAc2(tin(II) acetate), CsAc (Cesium acetate), FAAc(formamidinium acetate) 및 MAAc(methylammonium acetate)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 것을 특징으로 하는 주석계 페로브스카이트 적층체. |

| 11 | 제1항에 있어서,상기 주석계 페로브스카이트 적층체가 트랜지스터, 태양전지, 발광 다이오드, 포토 다이오드 또는 포토센서에 사용하기 위한 것을 특징으로 하는 주석계 페로브스카이트 적층체. |

| 12 | 제1항에 있어서,상기 반도체층의 두께가 10 내지 500nm의 범위인 것을 특징으로 하는 주석계 페로브스카이트 적층체. |

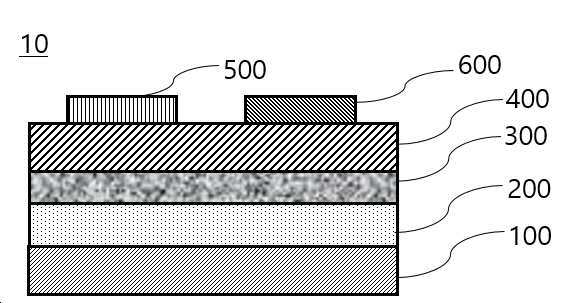

| 13 | 제1항에 있어서,상기 소수성층이 표면에 댕글링 본드(dangling bond)를 갖고 있지 않는 것을 특징으로 하는 주석계 페로브스카이트 적층체. |

| 14 | 게이트 전극(100);상기 게이트 전극 상에 형성된 절연층(200);상기 절연층 상에 형성되고, 소수성 2차원 물질을 포함하는 소수성층(300);상기 소수성층 상에 형성되고, 주석계 페로브스카이트를 포함하는 반도체층(400); 및 상기 반도체층 상에 서로 이격되어 형성된 소스 전극(500) 및 드레인 전극(600);을 포함하는 박막 트랜지스터(10). |

| 15 | (a) 게이트 전극(100) 및 상기 게이트 전극(100) 상에 형성된 절연층(200)을 포함하는 기판을 공급하는 단계; (b) 상기 기판의 절연층(200) 상에 소수성 2차원 물질을 포함하는 소수성층(300)을 형성하는 단계;(c) 상기 소수성층(300) 상에 주석계 페로브스카이트를 포함하는 반도체층(400)을 형성하는 단계; 및(d) 상기 반도체층(400) 상에 소스 전극(500) 및 드레인 전극(600)을 서로 이격되게 형성하는 단계;를포함하는 박막트랜지스터의 제조방법. |

| 16 | 제15항에 있어서,상기 단계 (b)가,(b-1) 금속포일 상에 소수성 2차원 물질을 포함하는 금속포일-소수성층을 형성하는 단계;(b-2) 상기 소수성층 상에 고분자를 포함하는 고분자 코팅층을 형성하여 금속포일-소수성층-고분자코팅층을 제조하는 단계;(b-3) 상기 금속포일-소수성층-고분자코팅층의 금속포일을 에칭하여 소수성층-고분자코팅층을 제조하는 단계;(b-4) 상기 소수성층-고분자 코팅층을 게이트 전극-절연층을 포함하는 기판 상에 올려 게이트 전극-절연층-소수성층-고분자코팅층을 제조하는 단계; 및(b-5) 상기 게이트 전극-절연층-소수성층-고분자코팅층을 유기용매에 함침하여 고분자코팅층을 용해시켜 게이트 전극(100)-절연층(200)-소수성층(300)을 제조하는 단계;를 포함하는 것을 특징으로 하는 박막 트랜지스터의 제조방법. |

| 17 | 제16항에 있어서,상기 단계(b)가 단계(b-2) 전에,(b'-2) 상기 금속포일의 양면 상에 소수성층이 형성되고, 상기 양면 중 한 어느 한 면 상에 형성된 소수성층을 CF4 플라즈마 처리하는 단계;를 추가로 포함하는 것을 특징으로 하는 박막트랜지스터의 제조방법. |

| 18 | 제16항에 있어서,상기 단계(b-1)이 화학기상증착법(CVD)에 의해 수행되는 것을 특징으로 하는 박막 트랜지스터의 제조방법. |

| 19 | 제16항에 있어서,상기 단계(b-2)가 스핀코팅에 의해 수행되는 것을 특징으로 하는 박막 트랜지스터의 제조방법. |

| 20 | 제15항에 있어서,상기 단계(c)가 열 증착(Thermal Evaporation), 스핀코팅, 바코팅, 스프레이(Spray), 잉크젯(Inkjet), 플렉소그라피(Flexography), 스크린(Screen), Dip-Coating, 화학 증착(CVD), 원자층 증착(ADL), 스퍼터링 및 그라비어(Gravure)로 이루어진 군으로부터 선택된 어느 하나에 의해 수행되는 것을 특징으로 하는 박막 트랜지스터의 제조방법. |