| 번호 | 청구항 |

|---|---|

| 1 | (a) 황 원자(S) 및 셀레늄 원자(Se)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 칼코겐 원자 및 텔루륨 원자(Te)를 포함하는 타겟을 제공하는 단계; 및(b) 아르곤 가스 및 산소 가스를 포함하는 혼합 기체의 분위기 하에서 상기 타겟을 사용하여 스퍼터링 방법으로 기판 상에 공증착(co-deposition)하여 비정질(amourphous) p형 반도체를 포함하는 반도체 박막을 제조하는 단계;를 포함하는 반도체 박막의 제조방법. |

| 2 | 제1항에 있어서,상기 단계(a)가 (a-1) 텔루륨 원자(Te)를 포함하는 제1 타겟을 제공하는 단계; 및(a-2) 황 원자(S) 및 셀레늄 원자(Se)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 칼코겐 원자를 포함하는 제2 타겟을 제공하는 단계;를 포함하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 3 | 제1항에 있어서,상기 단계(a)가 (a') 황 원자(S) 및 셀레늄 원자(Se)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 칼코겐 원자 및 텔루륨 원자(Te)가 혼합된 혼합물을 포함하는 타겟을 제공하는 단계; 인 것을 특징으로 하는 반도체 박막의 제조방법. |

| 4 | 제2항에 있어서,상기 단계(b)가 (b-1) 아르곤 가스 분위기 하에서 아르곤 플라즈마를 방전시키는 단계; 및(b-2) 상기 아르곤 가스 및 산소 가스를 포함하는 혼합기체의 분위기 하에서 상기 아르곤 플라즈마를 상기 제1 타겟 및 상기 제2 타겟과 충돌시켜 상기 제1 타겟의 원자, 상기 제2 타겟의 원자 및 그들의 산화물 중 1종 이상을 상기 기판 상에 공증착하여 텔루륨 복합체를 포함하는 반도체 박막을 제조하는 단계;를 포함하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 5 | 제4항에 있어서,상기 단계(b-1)의 플라즈마 방전 압력이 1 내지 15 Pa인 것을 특징으로 하는 반도체 박막의 제조방법. |

| 6 | 제4항에 있어서,상기 단계(b-1) 또는 단계(b-2)에서 아르곤 가스와 산소 가스의 총 압력인 공정 작업 압력이 1 Pa 이하인 것을 특징으로 하는 반도체 박막의 제조방법. |

| 7 | 제4항에 있어서,상기 단계(b-1) 또는 단계(b-2)에서 아르곤 가스와 산소 가스의 총 유량이 5 내지 50 sccm인 것을 특징으로 하는 반도체 박막의 제조방법. |

| 8 | 제4항에 있어서,상기 단계(b)에서 상기 아르곤 가스와 상기 산소 가스의 전체 압력(PAr + PO2)에 대한 산소 가스 분압(PO2)의 비(PO2/(PAr+PO2))가 0 내지 50 %인 것을 특징으로 하는 반도체 박막의 제조방법. |

| 9 | 제4항에 있어서,상기 단계(b)에서 상기 아르곤 가스와 상기 산소 가스의 전체 압력(PAr + PO2)에 대한 산소 가스 분압(PO2)의 비(PO2/(PAr+PO2))를 조절하여 상기 비정질 p형 반도체의 산소 함량을 제어하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 10 | 제1항에 있어서,상기 단계(b)가 상온에서 수행되는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 11 | 제1항에 있어서,상기 반도체 박막의 제조방법이 단계(b) 후에(c) 상기 반도체 박막을 공기 중에서 200 내지 300 ℃의 온도로 어닐링(annealing)하는 단계;를 추가로 포함하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 12 | 제1항에 있어서,상기 비정질 p형 반도체가셀레늄 원자(Se) 및 황 원자(S)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 칼코겐 원자; 및텔루륨(Te) 원자 및 텔루륨 옥사이드를 포함하는 텔루륨 복합체;를 포함하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 13 | 제12항에 있어서,상기 칼코겐 원자가 상기 텔루륨 복합체와 합금된(alloyed) 것을 특징으로 하는 반도체 박막의 제조방법. |

| 14 | 제12항에 있어서,상기 p형 반도체가 아래 화학식 2로 표시되는 것을 특징으로 하는 반도체 박막의 제조방법.[화학식 1]TeOx:M상기 화학식 2에서,M은 황 원자(S) 또는 셀레늄 원자(Se)이고,x는 0.8≤x≤1.7이다. |

| 15 | 제12항에 있어서,상기 반도체의 텔루륨 원자가 Te4+의 이온화 상태, Te2+ 의 이온화 상태 및 Te0의 비이온화 상태를 포함하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 16 | 제12항에 있어서,상기 텔루륨 옥사이드가 일산화 텔루륨(TeO) 및 이산화 텔루륨(TeO2)를 포함하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 17 | 제1항에 있어서,상기 반도체가 산소 결핍 상태인 것을 특징으로 하는 반도체 박막의 제조방법. |

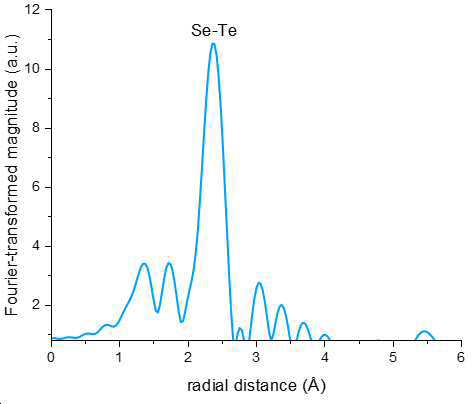

| 18 | (1) 게이트 전극 및 상기 게이트 전극 상에 위치하는 절연층을 포함하는 적층체를 준비하는 단계;(2) 상기 적층체의 절연층 상에 제1항에 따른 방법으로 제조되고, 반도체를 포함하는 반도체 박막을 형성하는 단계; 및(3) 상기 반도체 박막 상에 소스 전극 및 드레인 전극을 형성하는 단계;를 포함하는 것인 박막트랜지스터의 제조방법. |

| 19 | 제1항에 따른 반도체 박막의 제조방법에 의해 제조된 반도체 박막이고,상기 반도체 박막이 비정질 p형 반도체를 포함하고, 상기 비정질 p형 반도체가셀레늄 원자(Se) 및 황 원자(S)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 칼코겐 원자; 및텔루륨(Te) 원자 및 텔루륨 옥사이드를 포함하는 텔루륨 복합체;를 포함하는 것인, 반도체 박막. |