| 번호 | 청구항 |

|---|---|

| 1 | (a) 인듐, 셀레늄 및 In2Se3로 이루어진 군으로부터 선택된 1종 이상의 증착 소스를 열증발(thermal evaporation)의 증착 방법으로 기판 상에 증착하여 코팅층을 형성하는 단계; 및(b) 상기 코팅층을 열처리로 어닐링(annealing)하여 화학식 1로 표시되는 인듐-셀레나이드 화합물을 포함하는 반도체 박막을 제조하는 단계;를 포함하는 반도체 박막의 제조방법:[화학식 1]InxSey상기 화학식 1에서,x는 0003c#x≤3이고,y는 0003c#y≤4이다. |

| 2 | 제1항에 있어서,상기 화학식 1의 화합물이 In2Se3으로 표시되는 화합물을 포함하는 것을 특징으로 하는 반도체 박막의 제조방법: |

| 3 | 제1항에 있어서,상기 인듐-셀레나이드 화합물이 κ상(kappa phase)의 인듐-셀레나이드 화합물을 포함하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 4 | 제1항에 있어서,상기 반도체 박막이 강유전성(ferroelectricity) 또는 상유전성(paraelectricity)을 갖는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 5 | 제1항에 있어서,상기 단계(a)의 증착 속도를 조절하여 상기 반도체 박막의 강유전성 또는 상유전성을 제어하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 6 | 제1항에 있어서,상기 단계(a)의 증착 속도를 증가시켜 상기 반도체 박막을 상유전성으로부터 강유전성으로 전환시키는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 7 | 제1항에 있어서,상기 단계(a)의 증착 속도가 0.1 내지 3.4 Å s-1인 것을 특징으로 하는 반도체 박막의 제조방법. |

| 8 | 제1항에 있어서,상기 단계(a)의 상기 코팅층의 두께를 조절하여 상기 반도체 박막의 강유전성 또는 상유전성을 제어하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 9 | 제1항에 있어서,상기 단계(a)의 상기 코팅층의 두께를 증가시켜 상기 반도체 박막을 상유전성으로부터 강유전성으로 전환시키는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 10 | 제1항에 있어서,상기 단계(b)의 상기 반도체 박막의 두께가 5 내지 50 nm인 것을 특징으로 하는 반도체 박막의 제조방법. |

| 11 | 제1항에 있어서,상기 단계(b)의 상기 코팅층을 어닐링함에 의해 κ상(kappa phase)을 갖는 인듐-셀레나이드 화합물을 포함하는 반도체 박막을 제조하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 12 | 제1항에 있어서,상기 단계(b)의 상기 코팅층의 어닐링을 200 내지 400 ℃에서 수행하는 것을 특징으로 하는 반도체 박막의 제조방법. |

| 13 | κ상(kappa phase)을 갖고 화학식 1로 표시되는 인듐-셀레나이드 화합물을 포함하는 반도체 박막.[화학식 1]InxSey상기 화학식 1에서,x는 0003c#x≤3이고,y는 0003c#y≤4이다. |

| 14 | 제13항에 있어서,상기 반도체 박막이 1.0 내지 2.0 eV의 밴드갭을 갖는 것을 특징으로 하는 반도체 박막. |

| 15 | 제13항에 있어서,상기 반도체 박막이 1x106 이상의 on/off 전류비와 10 cm2/Vs 이상의 전자 이동도를 갖는 것을 특징으로 하는 반도체 박막. |

| 16 | 제13항에 있어서,상기 반도체 박막에서 Se-In-Se-In-Se의 순서로 5개의 원자가 하나의 층을 이루는 것을 특징으로 하는 반도체 박막. |

| 17 | 제13항에 있어서,상기 반도체 박막이 박막트랜지스터, 메모리소자, 태양전지, 발광 다이오드, 포토 다이오드 및 포토 센서로 이루어진 군으로부터 선택된 어느 하나의 n-채널에 사용하기 위한 것을 특징으로 하는 반도체 박막. |

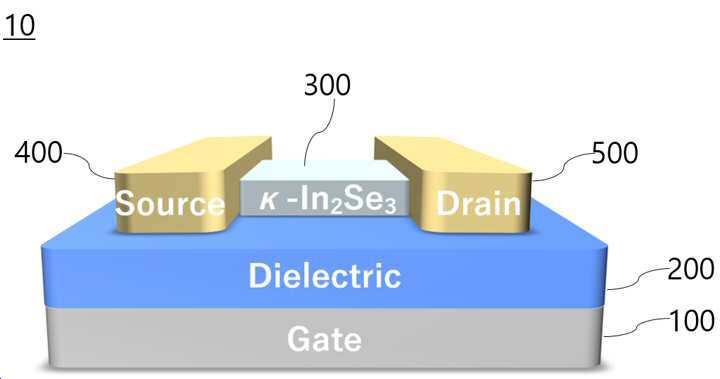

| 18 | 게이트 전극(100);상기 게이트 전극 상에 위치하는 절연층(200);상기 절연층 상에 위치하고, 화학식 1로 표시되는 인듐-셀레나이드 화합물을 포함하는 반도체 박막(300); 및상기 반도체 박막 상에 서로 이격되어 위치하는 소스 전극(400) 및 드레인 전극(500);을 포함하는 박막 트랜지스터(10).[화학식 1]InxSey상기 화학식 1에서,x는 0003c#x≤3이고,y는 0003c#y≤4이다. |

| 19 | 제18항에 있어서,상기 반도체 박막이 κ상(kappa phase)의 인듐-셀레나이드를 포함하는 것을 특징으로 하는 박막 트랜지스터. |

| 20 | 제17항에 있어서,상기 게이트 전극이 n-도핑된 실리콘(n-doped Si), p-도핑된 실리콘(p-doped Si), 금(Au), 은(Ag), 백금(Pt), 티타늄(Ti), 알루미늄(Al), 텅스텐(W), 마그네슘(Mg), 칼슘(Ca), 이터븀(Yb), 크롬(Cr), 니켈(Ni), 몰리브덴(Mo), 산화금, 산화백금, 산화은, 산화팔라듐, 산화철, 그래핀(graphene), 탄소나노튜브(carbon nano tube, CNT), 은 나노와이어(Ag nanowire, Ag NW), 인듐 틴 옥사이드(Indium tin oxide) 및 폴리(3,4-에틸렌디옥시티오펜) 폴리스티렌 설폰산(poly(3,4-ethylenedioxythiophene) polystyrene sulfonate, PEDOT:PSS)로 이루어진 군으로부터 선택된 1종 이상을 포함하는 것을 특징으로 하는 박막 트랜지스터. |