| 번호 | 청구항 |

|---|---|

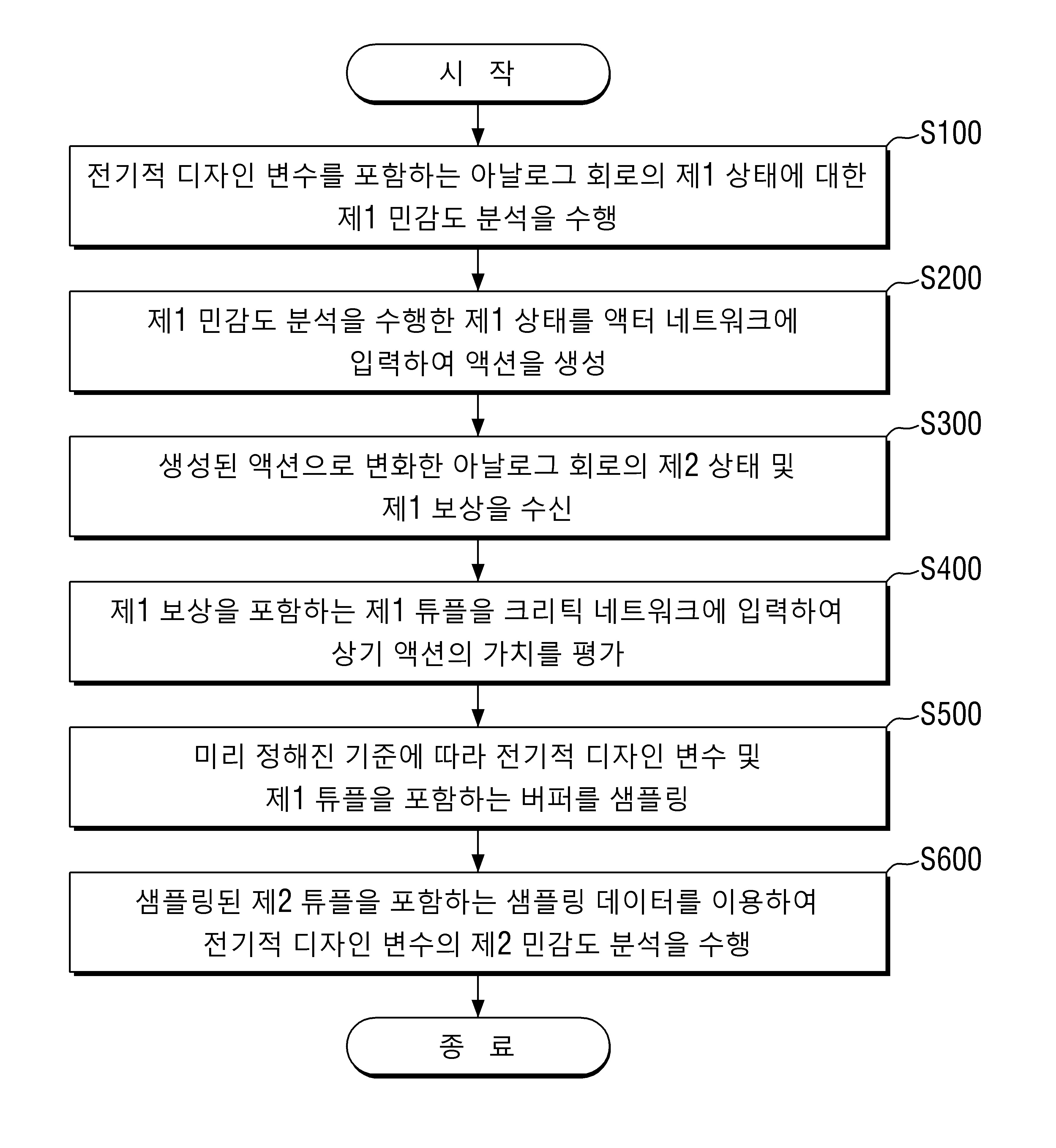

| 1 | 전기적 디자인 변수를 이용한 강화학습 기반의 아날로그 회로 최적화 방법에 있어서,상기 전기적 디자인 변수를 포함하는 상기 아날로그 회로의 제1 상태에 대한 제1 민감도 분석을 수행하는 단계;상기 제1 민감도 분석을 수행한 상기 제1 상태를 액터 네트워크에 입력하여 액션을 생성하는 단계;생성된 상기 액션으로 변화한 상기 아날로그 회로의 제2 상태 및 제1 보상을 수신하는 단계;상기 제1 보상을 포함하는 제1 튜플을 크리틱 네트워크에 입력하여 상기 액션의 가치를 평가하는 단계;미리 정해진 기준에 따라 상기 전기적 디자인 변수 및 상기 제1 튜플을 포함하는 버퍼를 샘플링하는 단계; 및샘플링된 제2 튜플을 포함하는 샘플링 데이터를 이용하여 상기 전기적 디자인 변수의 제2 민감도 분석을 수행하는 단계를 포함하는아날로그 회로 최적화 방법. |

| 2 | 제1 항에 있어서,상기 제1 튜플은, 상기 제1 상태, 상기 제2 상태, 제1 보상 및 상기 제1 상태를 임베딩한 제1 목표를 포함하는아날로그 회로 최적화 방법. |

| 3 | 제1 항에 있어서,상기 제1 민감도 분석을 수행하는 단계는,상기 아날로그 회로의 성능에 대한 복수의 동작 목표의 변화량과 상기 전기적 디자인 변수의 변화량 사이의 관계를 판단하는 단계와,상기 전기적 디자인 변수와 상기 복수의 동작 목표의 관계가 포함된 행렬을 생성하는 단계를 포함하는아날로그 회로 최적화 방법. |

| 4 | 제3 항에 있어서,상기 행렬은, 상기 복수의 동작 목표의 변화량에 대한 상기 복수의 동작 목표의 현재값과 상기 전기적 디자인 변수의 변화량에 대한 상기 제1 상태의 상기 전기적 디자인 변수의 값의 비례 관계를 포함하는아날로그 회로 최적화 방법. |

| 5 | 제4 항에 있어서,상기 복수의 동작 목표는, 상기 아날로그 회로의 이득, 전력, 위상 마진, 정정 시간, 단위이득 주파수(UGF), 동상신호 제거비(CMRR) 중 적어도 어느 하나를 포함하는아날로그 회로 최적화 방법. |

| 6 | 제1 항에 있어서,상기 전기적 디자인 변수는, 상기 아날로그 회로의 직류 전류에 대한 상호 컨덕턴스를 포함하는아날로그 회로 최적화 방법. |

| 7 | 제6 항에 있어서,상기 전기적 디자인 변수는, 상기 아날로그 회로의 너비를 결정할 수 있는 길이를 더 포함하되,상기 너비는, 상기 길이와 상기 직류 전류에 대한 상호 컨덕턴스의 관계에서 도출될 수 있는아날로그 회로 최적화 방법. |

| 8 | 제7 항에 있어서,상기 전기적 디자인 변수는, 상기 아날로그 회로의 바이어스 전압, 바이어스 전류, 나머지 저항 및 커패시티를 더 포함하는아날로그 회로 최적화 방법. |

| 9 | 제1 항에 있어서,상기 액션을 생성하는 단계는,상기 전기적 디자인 변수의 목표값과 상기 제1 상태의 차이와 동일한 제1 변화량을 입력하는 단계와,미리 정해진 범위 내에 포함된 상기 액션을 생성하는 단계를 포함하는아날로그 회로 최적화 방법. |

| 10 | 제1 항에 있어서,상기 액션의 가치를 평가하는 단계는,상기 제1 상태 및 상기 제2 상태를 하나의 벡터로 나타낸 제1 목표를 생성하는 단계와,상기 제1 상태와 상기 제1 목표를 연결하는 단계와,연결된 상기 제1 상태 및 상기 제1 목표를 상기 크리틱 네트워크에 입력하는 단계를 포함하는아날로그 회로 최적화 방법. |

| 11 | 제1 항에 있어서,상기 버퍼를 샘플링하는 단계는,미리 정해진 기준에 따라 상기 제1 튜플을 포함하는 복수의 튜플을 정렬하는 단계와,상기 정렬된 복수의 튜플의 제1 부분을 샘플링하여 제1 샘플링 데이터를 생성하는 단계와,상기 제1 부분을 제외한 상기 복수의 튜플을 샘플링하여 제2 샘플링 데이터를 생성하는 단계와,상기 제1 샘플링 데이터와 상기 제2 샘플링 데이터를 결합하여 상기 샘플링 데이터를 생성하는 단계를 포함하는아날로그 회로 최적화 방법. |

| 12 | 제11 항에 있어서,상기 복수의 튜플을 정렬하는 단계는, 상기 아날로그 회로의 길이를 기준으로 상기 복수의 튜플을 정렬하는 단계를 포함하는아날로그 회로 최적화 방법. |

| 13 | 제11 항에 있어서,상기 복수의 튜플을 정렬하는 단계는, 상기 아날로그 회로의 길이에 대한 상기 아날로그 회로의 너비를 기준으로 상기 복수의 튜플을 정렬하는 단계를 포함하는아날로그 회로 최적화 방법. |