| 번호 | 청구항 |

|---|---|

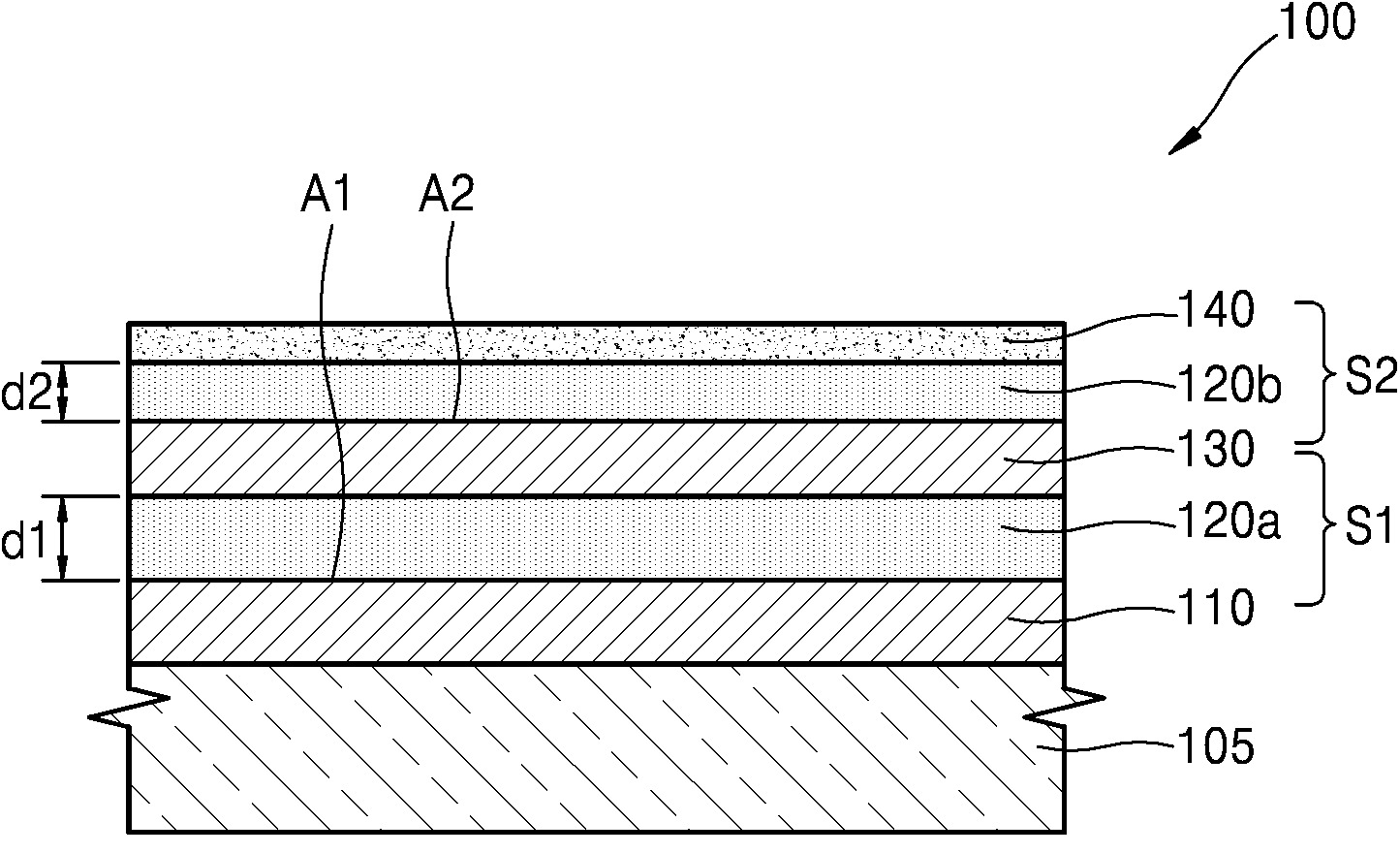

| 1 | 기판;상기 기판 상의 제어 게이트 전극층;상기 제어 게이트 전극층 상의 제 1 강유전체층;상기 제 1 강유전체층 상의 내부 전극층;상기 내부 전극층 상의 제 2 강유전체층; 및상기 제 2 강유전체층 상의 반도체 채널층을 포함하고,상기 제어 게이트 전극층, 상기 제 1 강유전체층 및 상기 내부 전극층의 제 1 적층 구조의 제 1 커패시턴스에 대한 상기 내부 전극층, 상기 제 2 강유전체층 및 상기 반도체 채널층의 제 2 적층 구조의의 제 2 커패시턴스의 비는 5 이상이고,상기 제 1 적층 구조에서 상기 제어 게이트 전극층의 상면과 상기 제 1 강유전체층이 접하는 제 1 면적에 대한 상기 제 2 적층 구조에서 상기 내부 전극층의 상면과 상기 제 2 강유전체층이 접하는 제 2 면적의 비는 1 이상이고,상기 제 1 커패시턴스에 대한 상기 제 2 커패시턴스의 비는 10 이상인,강유전체 트랜지스터. |

| 2 | 삭제 |

| 3 | 삭제 |

| 4 | 삭제 |

| 5 | 제 1 항에 있어서,8V 이상의 메모리 윈도우를 갖기 위해서, 상기 제 1 적층 구조에서 상기 제어 게이트 전극층의 상면과 상기 제 1 강유전체층이 접하는 제 1 면적에 대한 상기 제 2 적층 구조에서 상기 내부 전극층의 상면과 상기 제 2 강유전체층이 접하는 제 2 면적의 비는 5 이상인,강유전체 트랜지스터. |

| 6 | 제 1 항에 있어서,상기 제 1 강유전체층 및 상기 제 2 강유전체층은 동일한 물질로 형성된, 강유전체 트랜지스터. |

| 7 | 기판;상기 기판 상의 수직하게 연장된 원통 형태의 반도체 채널층;상기 반도체 채널층의 외주면을 한바퀴 둘러싸는 내부 강유전체층;상기 내부 강유전체층의 외주면을 한바퀴 둘러싸는 내부 전극층;상기 내부 전극층의 외주면을 한바퀴 둘러싸는 외부 강유전체층; 및상기 외부 강유전체층의 외주면을 한바퀴 둘러싸는 제어 게이트 전극층을 포함하고,상기 제어 게이트 전극층, 상기 외부 강유전체층 및 상기 내부 전극층의 제 1 적층 구조의 제 1 커패시턴스에 대한 상기 내부 전극층, 상기 제 내부 강유전체층 및 상기 반도체 채널층의 제 2 적층 구조의의 제 2 커패시턴스의 비는 5 이상이고,상기 내부 전극층은 외측으로 한바퀴 홈이 파진 원통 형상을 갖고,상기 외부 강유전체층은 상기 내부 전극층의 상기 홈 내에 형성되고,상기 제어 게이트 전극층은 상기 홈을 채우도록 상기 외부 강유전체층의 외측에 형성되는,강유전체 트랜지스터. |

| 8 | 제 7 항에 있어서,7V 이상의 메모리 윈도우를 갖기 위해서, 상기 제 1 커패시턴스에 대한 상기 제 2 커패시턴스의 비는 6 이상인, 강유전체 트랜지스터. |

| 9 | 제 7 항에 있어서,상기 제 1 커패시턴스에 대한 상기 제 2 커패시턴스의 비를 조절하기 위하여, 상기 내부 강유전체층의 두께를 조절하는, 강유전체 트랜지스터. |

| 10 | 삭제 |