| 번호 | 청구항 |

|---|---|

| 3 | 제 1 항에 있어서,상기 요철부는 홈부로서, 상기 강유전체층의 가운데 영역이 가장 얇은 두께를 갖도록 점진적으로 단차가 형성된,강유전체 박막 트랜지스터. |

| 4 | 제 1 항에 있어서,상기 요철부는 돌출부로서, 상기 강유전체층의 가운데 영역이 가장 두꺼운 두께를 갖도록 점진적으로 단차가 형성된,강유전체 박막 트랜지스터. |

| 5 | 제 1 항에 있어서,상기 강유전체층은 지르코늄(Zr), 알루미늄(Al), 실리콘(Si), 이트륨(Y), 가돌리늄(Gd) 및 란타늄(La) 중 적어도 하나가 첨가된 하프늄 산화물을 포함하는,강유전체 박막 트랜지스터. |

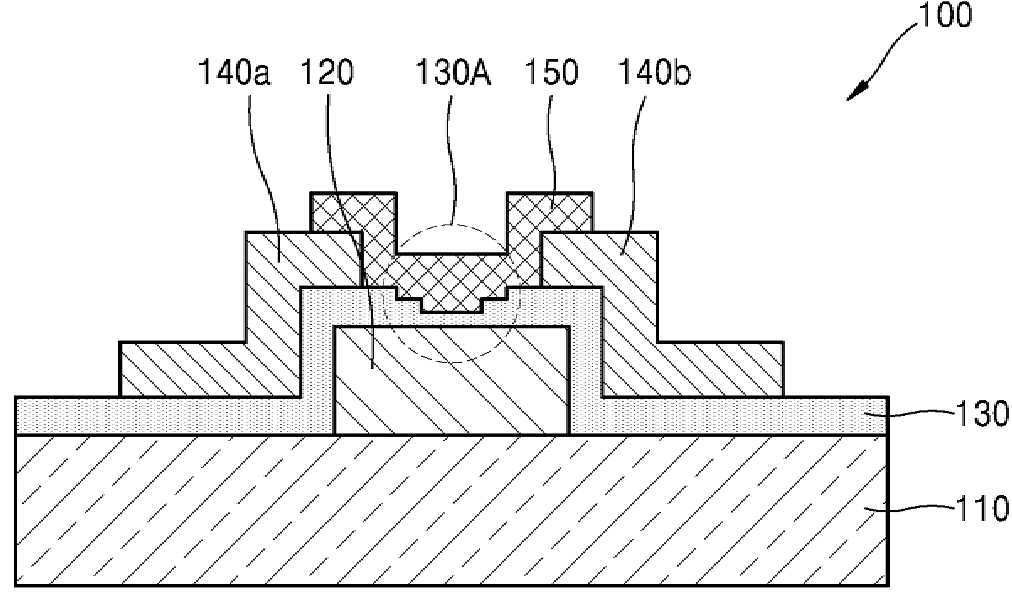

| 1 | 기판;상기 기판 상에 형성된 게이트 전극층;상기 게이트 전극 상에 형성되고, 하프늄계 산화물을 포함하며, 일부에 적어도 2개 이상의 단차가 형성되는 요철부를 포함하는 강유전체층;상기 강유전체층 상에 형성되고 산화물 반도체를 포함하는 반도체 채널층;상기 게이트 전극층의 일측에서 상기 반도체 채널층에 연결된 드레인 전극층; 및 상기 게이트 전극층의 타측에서 상기 반도체 채널층에 연결된 소스 전극층;을 포함하는,강유전체 박막 트랜지스터. |

| 2 | 제 1 항에 있어서,상기 요철부는 상기 강유전체층 및 상기 반도체 채널층이 서로 맞닿는 부분에 형성된,강유전체 박막 트랜지스터. |

| 6 | 제 1 항에 있어서,상기 반도체 채널층은 n형 산화물 반도체 또는 p형 산화물 반도체를 포함하고,상기 n형 산화물 반도체는 인듐산화물(In2O3), 아연산화물(ZnOx), 인듐주석산화물(InSnOx), 인듐아연산화물(InZnOx), 인듐갈륨산화물(InGaOx), 아연주석산화물(ZnSnOx), 알루미늄아연산화물(AlZnOx), 인듐갈륨아연산화물(InGaZnOx), 갈륨아연산화물(GaZnOx), 인듐아연주석산화물(InZnSnOx), 인듐아연주석산화물(InZnSnOx) 및 하프늄인듐아연산화물(HfInZnOx) 중 적어도 하나를 포함하고,상기 p형 산화물 반도체는 구리산화물(CuOx), 니켈산화물(NiOx), 주석산화물(SnOx), 망간산화물(MnOx), 구리알루미늄산화물(CuAlOx), 구리갈륨산화물(CuGaOx) 및 구리크롬산화물(CuCrOx) 중 적어도 하나를 포함하는,강유전체 박막 트랜지스터. |

| 7 | 제 1 항에 있어서,상기 게이트 전극층, 상기 드레인 전극층 및 상기 소스 전극층은 금속 또는 투명 도전성 산화물을 포함하는,강유전체 박막 트랜지스터. |

| 8 | 제 7 항에 있어서,상기 투명 도전성 산화물은 인듐산화물(InOx), 아연산화물(ZnOx), 인듐주석산화물(InSnOx), 인듐아연산화물(InZnOx), 인듐갈륨산화물(InGaOx), 아연주석산화물(ZnSnOx), 알루미늄아연산화물(AlZnOx), 인듐갈륨아연산화물(InGaZnOx), 갈륨아연산화물(GaZnOx), 인듐아연주석산화물(InZnSnOx), 인듐아연주석산화물(InZnSnOx), 하프늄인듐아연산화물(HfInZnOx), 구리산화물(CuOx), 니켈산화물(NiOx), 주석산화물(SnOx), 망간산화물(MnOx), 구리알루미늄산화물(CuAlOx), 구리갈륨산화물(CuGaOx) 및 구리크롬산화물(CuCrOx) 중 적어도 하나를 포함하는,강유전체 박막 트랜지스터. |

| 9 | 제 1 항에 있어서,상기 게이트 전극층, 상기 드레인 전극층 및 상기 소스 전극층은 금속 또는 금속 질화물을 포함하는,강유전체 박막 트랜지스터. |

| 10 | 제 1 항에 있어서,상기 드레인 전극층 및 상기 소스 전극층은 상기 강유전체층 상에 이격되게 형성되고,상기 반도체 채널층의 일측은 상기 강유전체층 상에서부터 상기 드레인 전극층의 단부 상으로 연장되고, 상기 반도체 채널층의 타측은 상기 강유전체층 상에서부터 상기 소스 전극층의 단부 상으로 연장되는,강유전체 박막 트랜지스터. |

| 11 | 게이트 전극층, 일부에 적어도 2개 이상의 단차가 형성되는 요철부를 포함하는 강유전체층 및 반도체 채널층을 포함하는 강유전체 박막 트랜지스터의 멀티레벨 동작방법으로서,상기 강유전체층의 분극 레벨을 멀티레벨로 제어하기 위하여, 펄스 진폭을 상이하게 상기 게이트 전극층에 프로그램 전압을 인가하여 상기 소자의 펄스 진폭 및 펄스 폭에 따른 문턱전압(Vth) 변화를 분석하는 단계; 및 상기 문턱전압이 감소하는 영역과 일정하게 유지되는 영역을 확인하고, 상기 문턱전압이 일정하게 유지되는 영역에서의 펄스 진폭 및 펄스 폭을 선정하여 상기 소자의 멀티레벨 동작을 제어하는 단계를 포함하는,강유전체 박막 트랜지스터의 멀티레벨 동작방법. |

| 12 | 제 11 항에 있어서,상기 문턱전압 변화를 분석하는 단계 이전에, 상기 게이트 전극층에 소거 전압을 인가하는 소거 단계를 수행하는,강유전체 박막 트랜지스터의 멀티레벨 동작방법. |

| 13 | 제 11 항에 있어서,상기 문턱전압이 일정하게 유지되는 영역은 상기 강유전체층에 구비된 상기 요철부의 구조에 따라 형성되는,강유전체 박막 트랜지스터의 멀티레벨 동작방법. |