| 번호 | 청구항 |

|---|---|

| 4 | 제 1 항에 있어서,상기 충진 절연층 상에 상기 채널층의 상단에 연결되도록 비트 라인을 형성하는 단계를 더 포함하는, 3차원 강유전체 트랜지스터의 제조 방법. |

| 5 | 제 1 항에 있어서,상기 복수의 층간 절연층들 및 상기 충진 절연층은 실리콘 산화물을 포함하는, 3차원 강유전체 트랜지스터의 제조 방법. |

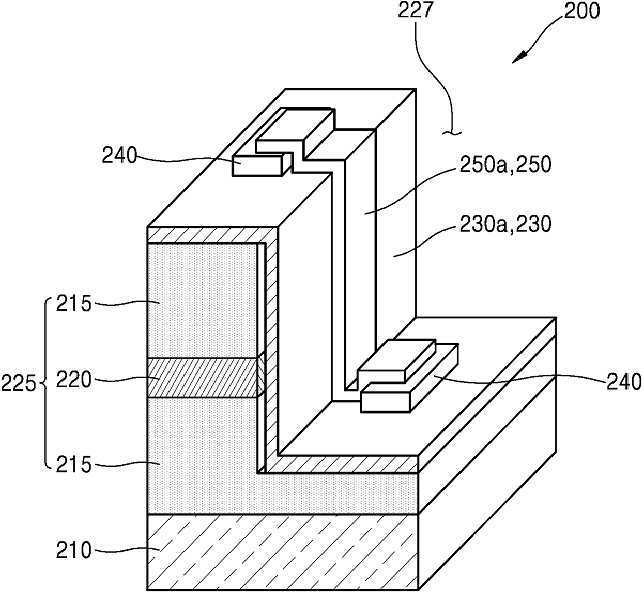

| 1 | 기판 상에 복수의 층간 절연층들 및 복수의 게이트 전극층들을 한층씩 교대로 형성하여 적층 구조를 형성하는 단계;상기 적층 구조에 적어도 하나의 수직 홀을 형성하는 단계;상기 적어도 하나의 수직 홀 내의 상기 적층 구조의 표면 상에 강유전체층을 형성하는 단계;상기 적어도 하나의 수직 홀 내의 상기 강유전체층 상에 채널층을 형성하는 단계; 및상기 적어도 하나의 수직 홀 내부를 채우도록 상기 채널층 상에 충진 절연층을 형성하는 단계를 포함하는,3차원 강유전체 트랜지스터의 제조 방법. |

| 2 | 제 1 항에 있어서,상기 복수의 게이트 전극층들은 폴리실리콘을 증착하여 형성하는, 3차원 강유전체 트랜지스터의 제조 방법. |

| 3 | 제 1 항에 있어서,상기 강유전체층 및 상기 채널층은 상기 적어도 하나의 수직 홀 내에서 상기 복수의 게이트 전극층들의 측벽들을 따라서 연장된 수직 부분을 포함하는, 3차원 강유전체 트랜지스터의 제조 방법. |

| 6 | 제 1 항에 있어서,상기 채널층은 산화물 반도체를 포함하고,상기 강유전체층은 하프늄 산화물, 또는 지르코늄(Zr), 알루미늄(Al), 실리콘(Si), 이트륨(Y), 가돌리늄(Gd) 및 란타늄(La) 중 적어도 하나가 첨가된 하프늄 산화물을 포함하는, 3차원 강유전체 트랜지스터의 제조 방법. |

| 7 | 제 1 항에 있어서,상기 복수의 게이트 전극층들은 복수의 워드 라인들로 동작하고,상기 채널층, 상기 강유전체층 및 상기 복수의 게이트 전극층들은 상기 적어도 하나의 수직 홀을 따라서 연장된 낸드셀을 구성하는, 3차원 강유전체 트랜지스터의 제조 방법. |

| 8 | 기판;상기 기판 상에 복수의 층간 절연층들 및 복수의 게이트 전극층들이 한층씩 교대로 형성되고, 적어도 하나의 수직 홀이 형성된 적층 구조;상기 적어도 하나의 수직 홀 내의 상기 적층 구조의 표면 상에 형성된 강유전체층;상기 적어도 하나의 수직 홀 내의 상기 강유전체층 상에 형성된 채널층; 및상기 적어도 하나의 수직 홀 내부를 채우도록 상기 채널층 상에 형성된 충진 절연층을 포함하고,상기 복수의 게이트 전극층들은 폴리실리콘을 증착하여 형성된,3차원 강유전체 트랜지스터. |

| 9 | 제 8 항에 있어서,상기 강유전체층 및 상기 채널층은 상기 적어도 하나의 수직 홀 내에서 상기 복수의 게이트 전극층들의 측벽들을 따라서 연장된 수직 부분을 포함하는, 3차원 강유전체 트랜지스터. |

| 10 | 제 8 항에 있어서,상기 채널층의 상단에 연결되도록 상기 충진 절연층 상에 형성된 비트 라인을 더 포함하는, 3차원 강유전체 트랜지스터. |