| 번호 | 청구항 |

|---|---|

| 21 | 제14 항에 있어서,상기 최종 연산값은, 상기 제1-1 및 제2-1 그룹값을 미리 정해진 방법으로 병합한 값을 포함하는,양자 회로 시뮬레이션 방법. |

| 22 | 제21 항에 있어서,상기 미리 정해진 방법은, 상기 제1-1 및 제2-1 그룹값의 크로네커 곱(Kronecker product)을 계산하는 것을 포함하는,양자 회로 시뮬레이션 방법. |

| 14 | 제13 항에 있어서,상기 최종 연산값을 계산하는 것은,상기 제1 및 제2 그룹을 상기 다중 게이트의 개수보다 큰 개수의 레이어로 분할하고,상기 제1 그룹의 상기 다중 게이트의 제1 경우의 수에 따른 제1-1 그룹값을 계산하고,상기 제2 그룹의 상기 다중 게이트의 상기 제1 경우의 수에 따른 제2-1 그룹값을 계산하고,상기 제1-1 및 제2-1 그룹값을 병합하는 것을 포함하는,양자 회로 시뮬레이션 방법. |

| 15 | 제14 항에 있어서,상기 제1-1 그룹값을 계산하는 것은,상기 제1 그룹의 상기 다중 게이트의 상기 제1 경우의 수와 상이한 제2 경우의 수에 따른 제1-4 그룹값을 계산하는 것을 더 포함하는,양자 회로 시뮬레이션 방법. |

| 16 | 제15 항에 있어서,상기 제1 연산값은, 상기 제1-1 그룹값 및 상기 제1-4 그룹값을 포함하는,양자 회로 시뮬레이션 방법. |

| 17 | 제15 항에 있어서,상기 제2-1 그룹값을 계산하는 것은,상기 제2 그룹의 상기 다중 게이트의 상기 제2 경우의 수에 따른 제2-4 그룹값을 계산하는 것을 더 포함하는,양자 회로 시뮬레이션 방법. |

| 18 | 제17 항에 있어서,상기 제2 연산값은, 상기 제2-1 그룹값 및 상기 제2-4 그룹값을 포함하는,양자 회로 시뮬레이션 방법. |

| 19 | 제17 항에 있어서,상기 최종 연산값은, 상기 제1-1 그룹값과 상기 제2-1 그룹값을 병합한 제1 중간 연산값과, 상기 제1-4 그룹값과 상기 제2-4 그룹값을 병합한 제4 중간 연산값을 더한 값을 포함하는,양자 회로 시뮬레이션 방법. |

| 1 | 메모리;상기 메모리와 연계되어 동작하는 프로세서를 포함하고,상기 프로세서는,적어도 둘 이상의 큐빗(qubit)과 상기 적어도 둘 이상의 큐빗을 연결하는 다중 게이트(gate)을 포함하는 제1 양자 회로의 가중치를 계산하고,상기 적어도 둘 이상의 큐빗을 2개의 그룹으로 나눌 때, 상기 가중치에 기초하여 상기 다중 게이트의 커팅수를 최소화하는 커팅 라인을 결정하고,상기 제1 양자 회로를 상기 커팅 라인에 의해 제1 그룹과 제2 그룹으로 분할하여 상기 적어도 둘 이상의 큐빗을 재배열한 제2 양자 회로를 결정하고,상기 제2 양자 회로에서 상기 제1 그룹의 제1 연산값과 제2 그룹의 제2 연산값을 병합하여 최종 연산값을 계산하고,상기 제2 양자 회로의 적어도 둘 이상의 큐빗을 상기 제1 양자 회로와 동일하게 재배열하는 것을 포함하는,양자 회로 시뮬레이션 장치. |

| 2 | 제1 항에 있어서,상기 제1 양자 회로의 가중치를 계산하는 것은,상기 제1 양자 회로에서 상기 적어도 둘 이상의 큐빗 중 하나를 연산하는 단일 게이트를 제거하고,상기 단일 게이트가 제거된 상기 제1 양자 회로에서 상기 다중 게이트를 카운팅하여 가중치를 결정하고,상기 가중치를 포함하는 가중치 그래프를 생성하는 것을 포함하는,양자 회로 시뮬레이션 장치. |

| 3 | 제2 항에 있어서,상기 큐빗은 제1 및 제2 큐빗을 포함하고,상기 가중치 그래프를 생성하는 것은, 상기 제1 및 제2 큐빗을 연결하는 제1 다중 게이트의 수를 표시하는 것을 포함하는,양자 회로 시뮬레이션 장치. |

| 4 | 제3 항에 있어서,상기 큐빗은 제3 큐빗을 더 포함하고,상기 가중치 그래프를 생성하는 것은,상기 제2 및 제3 큐빗을 연결하는 제2 다중 게이트의 수를 표시하고,상기 제3 및 제1 큐빗을 연결하는 제3 다중 게이트의 수를 표시하는 것을 더 포함하는,양자 회로 시뮬레이션 장치. |

| 5 | 제2 항에 있어서,상기 가중치 그래프는, 상기 다중 게이트에 대응하는 직선과 상기 가중치에 대응하는 숫자를 포함하는,양자 회로 시뮬레이션 장치. |

| 6 | 제2 항에 있어서,상기 커팅 라인을 결정하는 것은, 알고리즘에 따라 상기 다중 게이트의 상기 커팅수를 최소화하여 상기 양자 회로를 분할하는 선을 결정하는 것을 포함하는,양자 회로 시뮬레이션 장치. |

| 7 | 제6 항에 있어서,상기 알고리즘은, FM(Fiduccia Mattheyses) 알고리즘을 포함하는,양자 회로 시뮬레이션 장치. |

| 8 | 제6 항에 있어서,상기 커팅수는, 상기 가중치 그래프 내에서 상기 커팅 라인을 지나는 상기 다중 게이트의 수를 포함하는,양자 회로 시뮬레이션 장치. |

| 9 | 제6 항에 있어서,상기 제1 그룹의 큐빗 수는 제2 그룹의 큐빗 수보다 2 이상 큰,양자 회로 시뮬레이션 장치. |

| 10 | 제1 항에 있어서,상기 제2 양자 회로를 결정하는 것은,적어도 하나의 큐빗을 포함하는 상기 제1 및 제2 그룹으로 분할하고,상기 제1 및 제2 그룹을 상기 양자 회로 상에 그룹별로 재배열하는 것을 포함하는,양자 회로 시뮬레이션 장치. |

| 11 | 제1 항에 있어서,상기 최종 연산값을 계산하는 것은,상기 제1 및 제2 그룹을 미리 정해진 개수의 레이어로 분할하고,상기 제1 그룹의 상기 다중 게이트의 제1 경우의 수에 따른 제1-1 그룹값을 계산하고,상기 제2 그룹의 상기 다중 게이트의 상기 제1 경우의 수에 따른 제2-1 그룹값을 계산하고,상기 제1-1 및 제2-1 그룹값을 병합하는 것을 포함하는,양자 회로 시뮬레이션 장치. |

| 12 | 제11 항에 있어서,상기 미리 정해진 개수는, 상기 다중 게이트의 개수와 동일한,양자 회로 시뮬레이션 장치. |

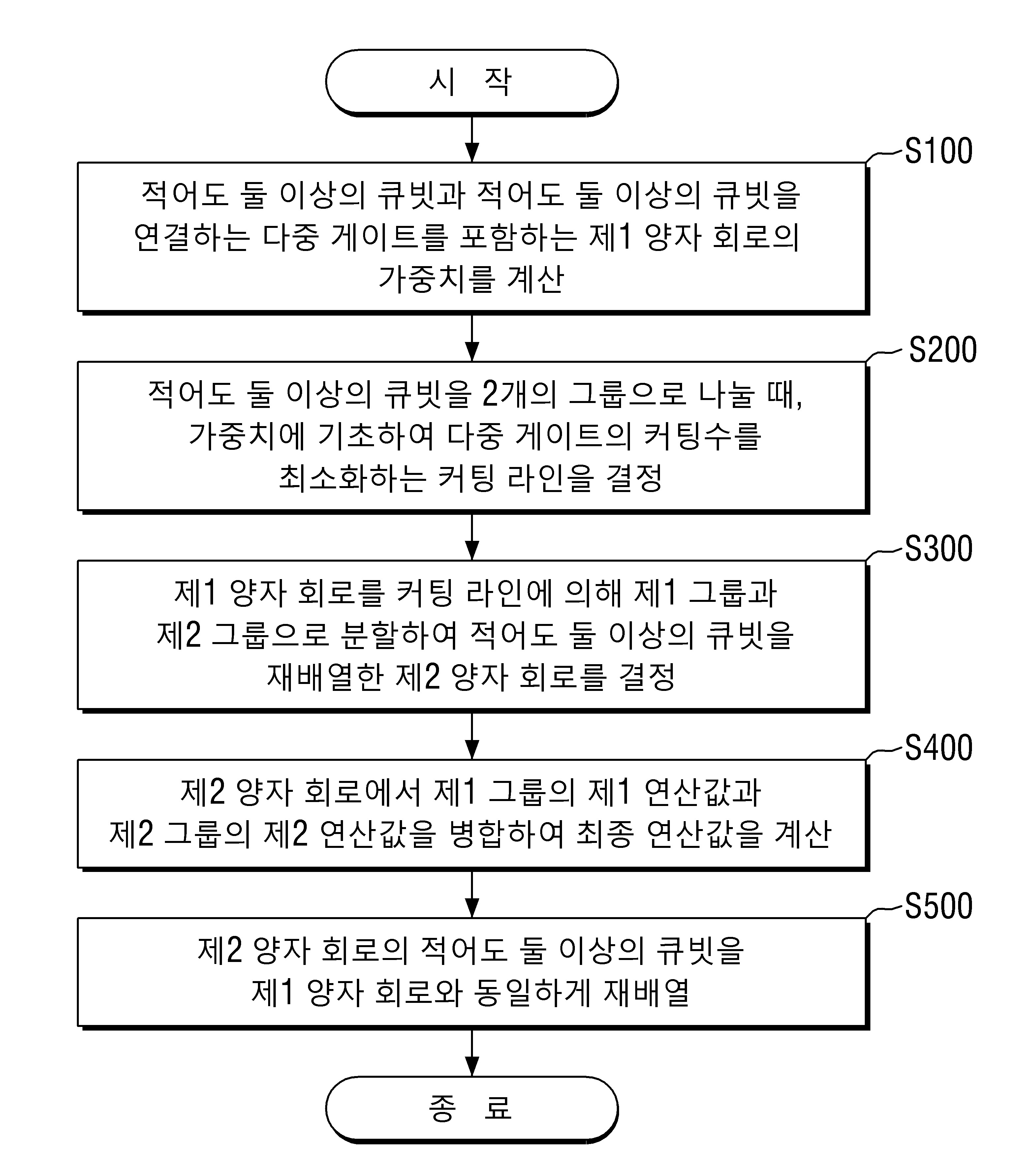

| 13 | 적어도 둘 이상의 큐빗과 상기 적어도 둘 이상의 큐빗(qubit)을 연결하는 다중 게이트(gate)을 포함하는 제1 양자 회로의 가중치를 계산하고,상기 적어도 둘 이상의 큐빗을 2개의 그룹으로 나눌 때, 상기 가중치에 기초하여 상기 다중 게이트의 커팅수를 최소화하는 커팅 라인을 결정하고,상기 제1 양자 회로를 상기 커팅 라인에 의해 제1 그룹과 제2 그룹으로 분할하여 상기 적어도 둘 이상의 큐빗을 재배열한 제2 양자 회로를 결정하고,상기 제2 양자 회로에서 상기 제1 그룹의 제1 연산값과 제2 그룹의 제2 연산값을 병합하여 최종 연산값을 계산하고,상기 제2 양자 회로의 적어도 둘 이상의 큐빗을 상기 제1 양자 회로와 동일하게 재배열하는 것을 포함하는,양자 회로 시뮬레이션 방법. |

| 20 | 제14 항에 있어서,상기 최종 연산값을 계산하는 것은, 상기 레이어에 깊이 우선 탐색(Depth-First Search, DFS)을 이용하는 것을 포함하는,양자 회로 시뮬레이션 방법. |