| 번호 | 청구항 |

|---|---|

| 11 | 제7항에 있어서,상기 정확도-전력 분석은 각각의 상기 부분 곱의 조합에 대하여 MAPE(mean absolute percentage error) 및 평균 소모 전력을 계산하는 것인, 6×6 근사 삼진 곱셈기. |

| 10 | 제7항에 있어서,상기 제3 2×2 근사 삼진 곱셈기(APPX+9)는한 개의 1×1 삼진 곱셈기(Tmul), 세 개의 1×1 근사 삼진 곱셈기(ATmul), 제2 오류 보상 회로, 한 개의 삼진 반가산기(THA), 한 개의 삼진 전가산기(TFA) 및 한 개의 삼진 Sum 게이트(TSum)로 구성되되,상기 제2 오류 보상 회로는 상기 두 개의 피연산자가 미리 결정된 수의 조합인 경우 오류의 편향을 감소시키기 위한 제2보상 값을 생성하는, 6×6 근사 삼진 곱셈기. |

| 1 | 각각이 1-트릿(trit)인 두 개의 피연산자에 대하여 근사 곱(APPX. product)을 계산하되, 상기 근사 곱은 하기의 진리표에 의해 결정되고, 삼진 곱셈의 부분 곱(partial product)을 감소시키기 위해 캐리(ACC. Carry)가 생략된(carry-truncated) 삼진 곱셈기인, 1×1 근사 삼진 곱셈기(ATMul). |

| 2 | 각각이 2-트릿인 두 개의 피연산자에 대하여 근사 삼진 곱셈을 수행하기 위한 2×2 근사 삼진 곱셈기(APPX)에 있어서,상기 두 피연산자의 최상위트릿(most significant trit, MST)끼리의 곱셈을 수행하는 1×1 삼진 곱셈기(Tmul);상기 두 피연산자의 상기 최상위트릿(MST)을 제외한 나머지 트릿의 조합에 대하여 근사 곱셈을 수행함으로써 세 개의 부분 곱을 계산하는 세 개의 1×1 근사 삼진 곱셈기(ATmul);상기 세 개의 부분 곱 중 상기 두 개의 피연산자의 최하위트릿(least significant trit, LST)끼리의 곱셈에 의한 부분 곱을 제외한 나머지 두 개의 부분 곱을 합산하는 제1 삼진 반가산기(THA);상기 제1 삼진 반가산기(THA)에서 출력된 캐리 및 상기 1×1 삼진 곱셈기(Tmul)에서 출력된 곱을 합산하는 제2 삼진 반가산기(THA); 및상기 제2 삼진 반가산기(THA)에서 출력된 캐리 및 상기 1×1 삼진 곱셈기(Tmul)에서 출력된 캐리를 합산하는 삼진 Sum 게이트(TSum)을 포함하는, 2×2 근사 삼진 곱셈기(APPX). |

| 3 | 각각이 2-트릿인 두 개의 피연산자에 대하여 근사 삼진 곱셈을 수행하기 위한 2×2 근사 삼진 곱셈기(APPX+6)에 있어서,상기 두 피연산자의 최상위트릿(most significant trit, MST)끼리의 곱셈을 수행하는 1×1 삼진 곱셈기(Tmul);상기 두 피연산자의 상기 최상위트릿(MST)을 제외한 나머지 트릿의 조합에 대하여 근사 곱셈을 수행함으로써 세 개의 부분 곱을 계산하는 세 개의 1×1 근사 삼진 곱셈기(ATmul);상기 두 개의 피연산자가 미리 결정된 수의 조합인 경우 오류의 중요도를 감소시키기 위한 제1 보상 값을 생성하는 제1 오류 보상 회로;상기 세 개의 부분 곱 중 상기 두 개의 피연산자의 최하위트릿(least significant trit, LST)끼리의 곱셈에 의한 부분 곱을 제외한 나머지 두 개의 부분 곱 및 상기 제1 보상 값을 합산하는 삼진 전가산기(TFA);상기 삼진 전가산기(TFA)에서 출력된 캐리 및 1×1 삼진 곱셈기(Tmul)에서 출력된 곱을 합산하는 삼진 반가산기(THA); 및상기 삼진 반가산기(THA)에서 출력된 캐리 및 1×1 삼진 곱셈기(Tmul)에서 출력된 캐리를 합산하는 삼진 Sum 게이트(TSum)를 포함하는, 2×2 근사 삼진 곱셈기(APPX+6). |

| 4 | 제3항에 있어서,상기 제1 보상 값은 6인, 2×2 근사 삼진 곱셈기(APPX+6). |

| 5 | 각각이 2-트릿인 두 개의 피연산자에 대하여 근사 삼진 곱셈을 수행하기 위한 2×2 근사 삼진 곱셈기(APPX+9)에 있어서,상기 두 피연산자의 최상위트릿(most significant trit, MST)끼리의 곱셈을 수행하는 1×1 삼진 곱셈기(Tmul);상기 두 피연산자의 상기 최상위트릿(MST)을 제외한 나머지 트릿의 조합에 대하여 근사 곱셈을 수행함으로써 세 개의 부분 곱을 계산하는 세 개의 1×1 근사 삼진 곱셈기(ATmul);상기 두 개의 피연산자가 미리 결정된 수의 조합인 경우 오류의 중요도를 감소시키기 위한 제2 보상 값을 생성하는 제2 오류 보상 회로;상기 세 개의 부분 곱 중 상기 두 개의 피연산자의 최하위트릿(least significant trit, LST)끼리의 곱셈에 의한 부분 곱을 제외한 나머지 두 개의 부분 곱을 합산하는 삼진 반가산기(THA);상기 1×1 삼진 곱셈기(Tmul)에서 출력된 곱, 상기 삼진 반가산기(THA)에서 출력된 캐리 및 상기 제2 보상 값을 합산하는 삼진 전가산기(TFA); 및상기 삼진 전가산기(TFA)에서 출력된 캐리 및 1×1 삼진 곱셈기(Tmul)에서 출력된 캐리를 합산하는 삼진 Sum 게이트(TSum)를 포함하는, 2×2 근사 삼진 곱셈기(APPX+9). |

| 6 | 제5항에 있어서,상기 제2 보상 값은 9인, 2×2 근사 삼진 곱셈기(APPX+9). |

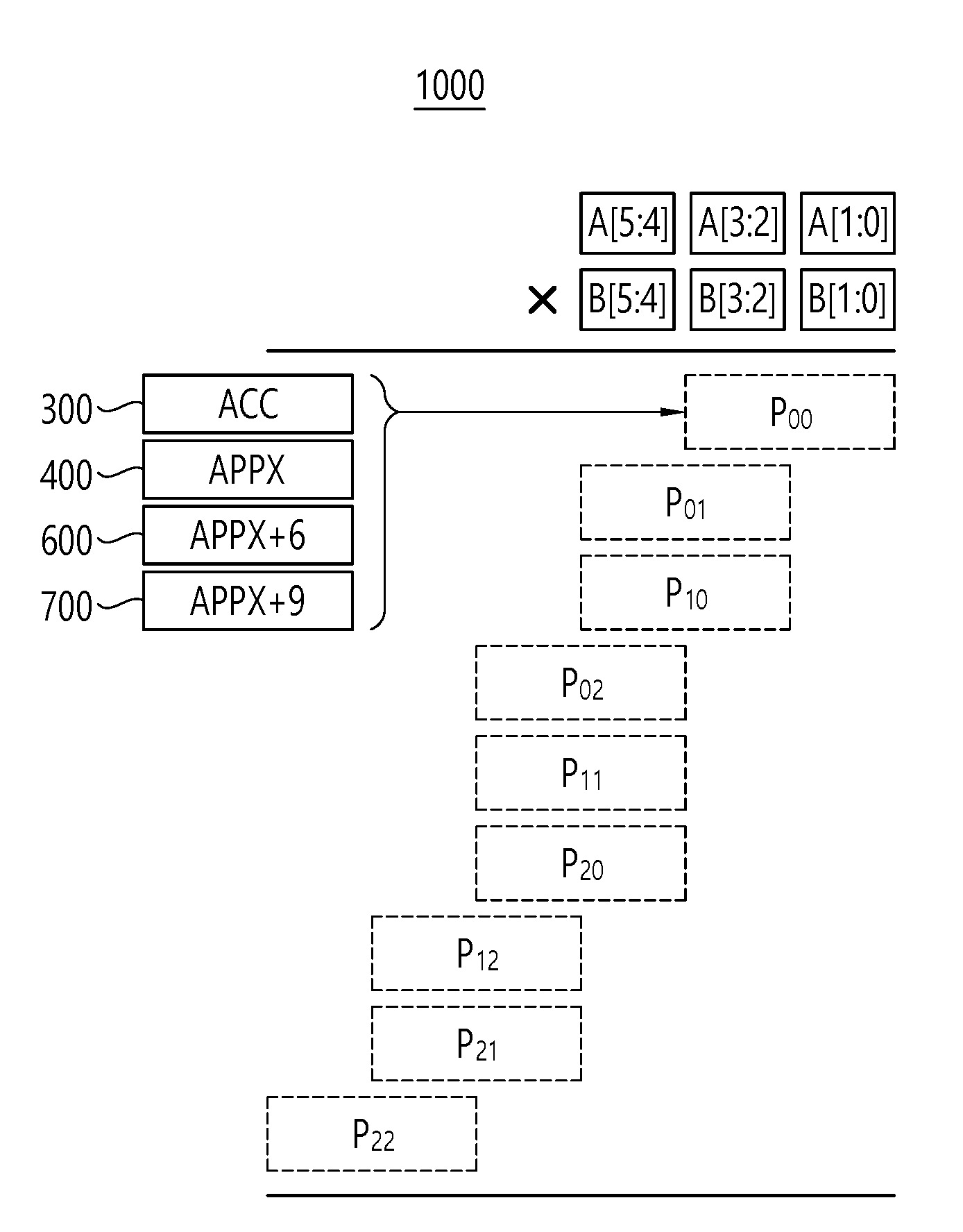

| 7 | 각각이 6-트릿인 두 개의 피연산자에 대하여 근사 삼진 곱셈을 수행하기 위한 6×6 근사 삼진 곱셈기에 있어서,상기 두 개의 피연산자에 대하여 복수의 부분 곱의 조합을 생성하고 - 각각의 상기 부분 곱의 조합은 2×2 삼진 곱셈기(ACC), 제1 2×2 근사 삼진 곱셈기(APPX), 제2 2×2 근사 삼진 곱셈기(APPX+6) 및 제3 2×2 근사 삼진 곱셈기(APPX+9) 중 어느 하나에 의해 계산됨 -,각각의 상기 부분 곱의 조합에 대하여 정확도-전력 분석을 수행하고,상기 복수의 부분 곱의 조합 중에서 목표 정확도를 갖는 제1 부분 곱의 조합을 선택하고,상기 제1 부분 곱의 조합 중에서 소모 전력이 최소인 제2 부분 곱의 조합을 선택하고,상기 제2 부분 곱의 조합을 합산하는, 6×6 근사 삼진 곱셈기. |

| 8 | 제7항에 있어서,상기 제1 2×2 근사 삼진 곱셈기(APPX)는한 개의 1×1 삼진 곱셈기(Tmul), 세 개의 1×1 근사 삼진 곱셈기(ATmul), 두 개의 삼진 반가산기(THA) 및 하나의 삼진 Sum 게이트(TSum)로 구성되는, 6×6 근사 삼진 곱셈기. |

| 9 | 제7항에 있어서,상기 제2 2×2 근사 삼진 곱셈기(APPX+6)는한 개의 1×1 삼진 곱셈기(Tmul), 세 개의 1×1 근사 삼진 곱셈기(ATmul), 제1 오류 보상 회로, 한 개의 삼진 전가산기(TFA), 한 개의 삼진 반가산기(THA) 및 한 개의 삼진 Sum 게이트(TSum)로 구성되되,상기 제1 오류 보상 회로는 상기 두 개의 피연산자가 미리 결정된 수의 조합인 경우 오류의 중요도를 감소시키기 위한 제1 보상 값을 생성하는, 6×6 근사 삼진 곱셈기. |