| 번호 | 청구항 |

|---|---|

| 20 | 제15항에 있어서,상기 산화물 반도체 층은 1015 cm-3 내지 1021 cm-3 의 전자 밀도를 갖는 반도체 메모리 소자. |

| 1 | 기판 상에 절연막들 및 전극들을 번갈아 적층하여 전극 구조체를 형성하는 것;상기 전극 구조체를 관통하는 채널 홀을 형성하는 것; 및상기 채널 홀을 채우는 수직 채널 구조체를 형성하는 것을 포함하되,상기 수직 채널 구조체를 형성하는 것은:상기 채널 홀의 내측벽 상에 강유전체 층을 형성하는 것;상기 강유전체 층 상에 산화물 반도체 층을 형성하는 것; 및상기 산화물 반도체 층 상에 어닐링 공정을 수행하는 것을 포함하는 반도체 메모리 소자의 제조방법. |

| 2 | 제1항에 있어서,상기 강유전체 층은 원자층 증착 공정을 이용하여 콘포멀하게 형성되는 반도체 메모리 소자의 제조방법. |

| 3 | 제1항에 있어서,상기 산화물 반도체 층을 형성하는 것은,상기 강유전체 층의 일부를 제거하여 상기 기판의 일부를 노출시키는 것; 및상기 강유전체 층 상에 원자층 증착 공정을 이용하여 상기 산화물 반도체 층을 콘포멀하게 형성하는 것을 포함하며,상기 산화물 반도체 층은 노출된 상기 기판의 일부와 접촉하는 반도체 메모리 소자의 제조방법. |

| 4 | 제3항에 있어서,상기 산화물 반도체 층은 소스로서 기능하는 상기 기판의 상면과 접촉하는 반도체 메모리 소자의 제조방법. |

| 5 | 제1항에 있어서,상기 강유전체 층의 강유전상은 상기 산화물 반도체 층 상에 수행되는 상기 어닐링 공정에 의해 유도되는 반도체 메모리 소자의 제조방법. |

| 6 | 제1항에 있어서,상기 어닐링 공정은 280℃ 내지 1000℃의 온도에서, 1초 내지 600초 동안 수행되는 반도체 메모리 소자의 제조방법. |

| 7 | 제1항에 있어서,상기 강유전체 층은 하프늄 산화물을 포함하되,지르코늄, 실리콘, 알루미늄, 가돌리늄 및 이트륨 중 적어도 어느 하나를 더 포함하는 반도체 메모리 소자의 제조방법. |

| 8 | 제1항에 있어서,상기 산화물 반도체 층은 In2O3, ZnO, IZO, IGO, ZTO, AZO, GZO, IGZO, IZTO 및 HIZO 중 적어도 어느 하나를 포함하는 반도체 메모리 소자의 제조방법. |

| 9 | 제1항에 있어서,상기 채널 홀의 잔부를 채우는 매립 절연 패턴을 형성하는 것;상기 매립 절연 패턴의 상부에 도전 패드를 형성하는 것을 더 포함하는 반도체 메모리 소자의 제조방법. |

| 10 | 제1항에 있어서,상기 강유전체 층 및 상기 산화물 반도체 층은 서로 물리적으로 접촉하는 반도체 메모리 소자의 제조방법. |

| 11 | 전극 상에 강유전체 층을 형성하는 것;상기 강유전체 층 상에 산화물 반도체 층을 형성하는 것;상기 산화물 반도체 층 상에 어닐링 공정을 수행하는 것; 및상기 산화물 반도체 층 상에 소스 전극 및 드레인 전극을 형성하는 것을 포함하되,상기 강유전체 층 및 상기 산화물 반도체 층은 서로 물리적으로 접촉하는 반도체 메모리 소자의 제조방법. |

| 12 | 제11항에 있어서, 상기 강유전체 층의 강유전상은 상기 산화물 반도체 층 상에 수행되는 상기 어닐링 공정에 의해 유도되는 반도체 메모리 소자의 제조방법. |

| 13 | 제11항에 있어서,상기 어닐링 공정은 280℃ 내지 1000℃의 온도에서, 1초 내지 600초 동안 수행되는 반도체 메모리 소자의 제조방법. |

| 14 | 제11항에 있어서,상기 산화물 반도체 층은 In2O3, ZnO, IZO, IGO, ZTO, AZO, GZO, IGZO, IZTO 및 HIZO 중 적어도 어느 하나를 포함하는 반도체 메모리 소자의 제조방법. |

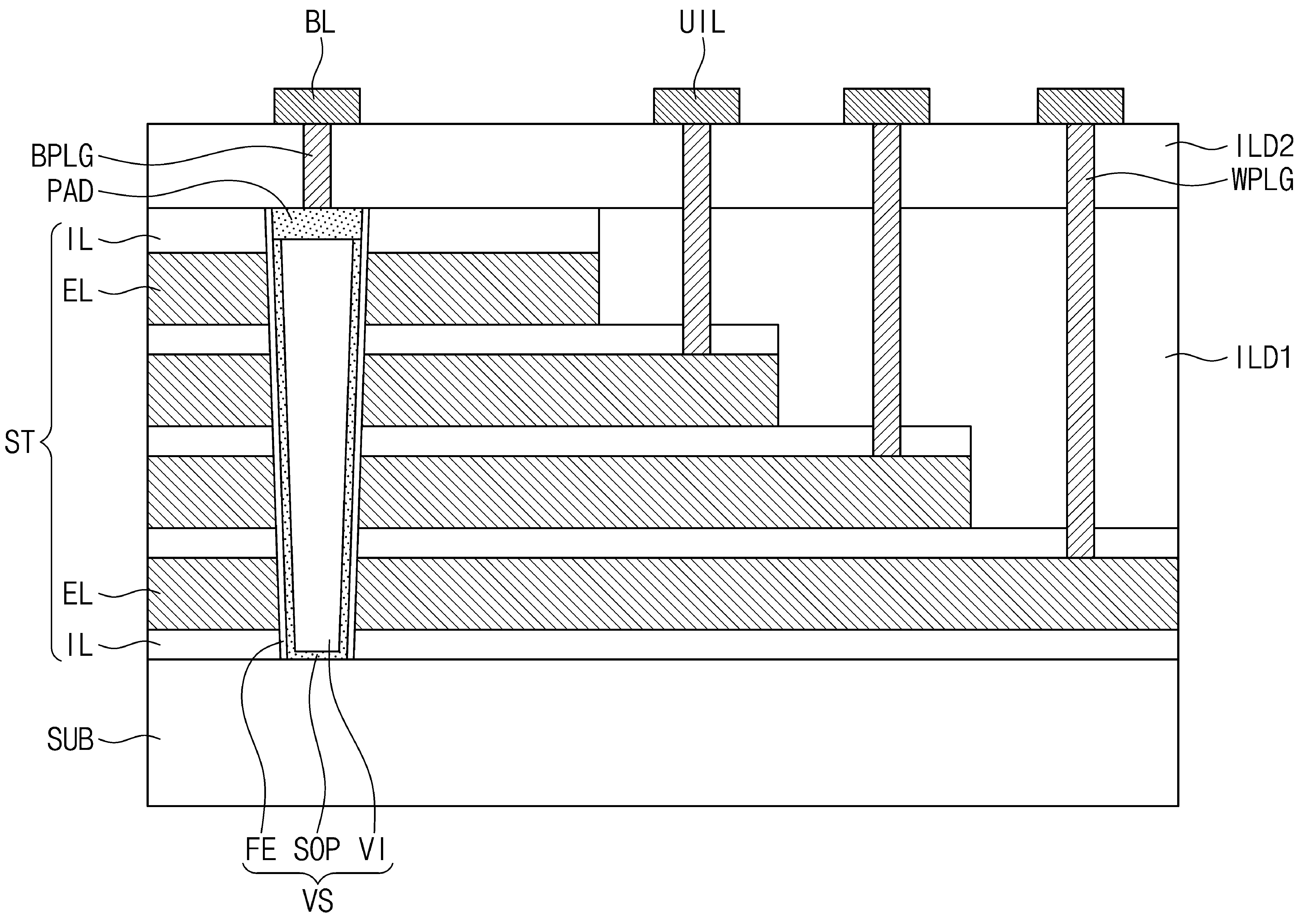

| 15 | 기판;상기 기판 상에 적층된 복수 개의 전극들을 포함하는 전극 구조체; 및상기 전극 구조체를 관통하는 수직 채널 구조체를 포함하되,상기 수직 채널 구조체는:수직하게 연장되는 산화물 반도체 층; 및상기 복수 개의 전극들과 상기 산화물 반도체 층 사이에 개재되는 강유전체 층을 포함하고,상기 강유전체 층 및 상기 산화물 반도체 층은 서로 물리적으로 접촉하고,상기 산화물 반도체 층은 상기 기판의 소스 반도체 막과 접촉하는 반도체 메모리 소자. |

| 16 | 제15항에 있어서,상기 강유전체 층의 강유전상은 상기 산화물 반도체 층에 의해 유도되는 반도체 메모리 소자. |

| 17 | 제15항에 있어서,상기 강유전체 층은 하프늄 산화물을 포함하되,지르코늄, 실리콘, 알루미늄, 가돌리늄 및 이트륨 중 적어도 어느 하나를 더 포함하는 반도체 메모리 소자. |

| 18 | 제15항에 있어서,상기 산화물 반도체 층은 In2O3, ZnO, IZO, IGO, ZTO, AZO, GZO, IGZO, IZTO 및 HIZO 중 적어도 어느 하나를 포함하는 반도체 메모리 소자. |

| 19 | 삭제 |