| 번호 | 청구항 |

|---|---|

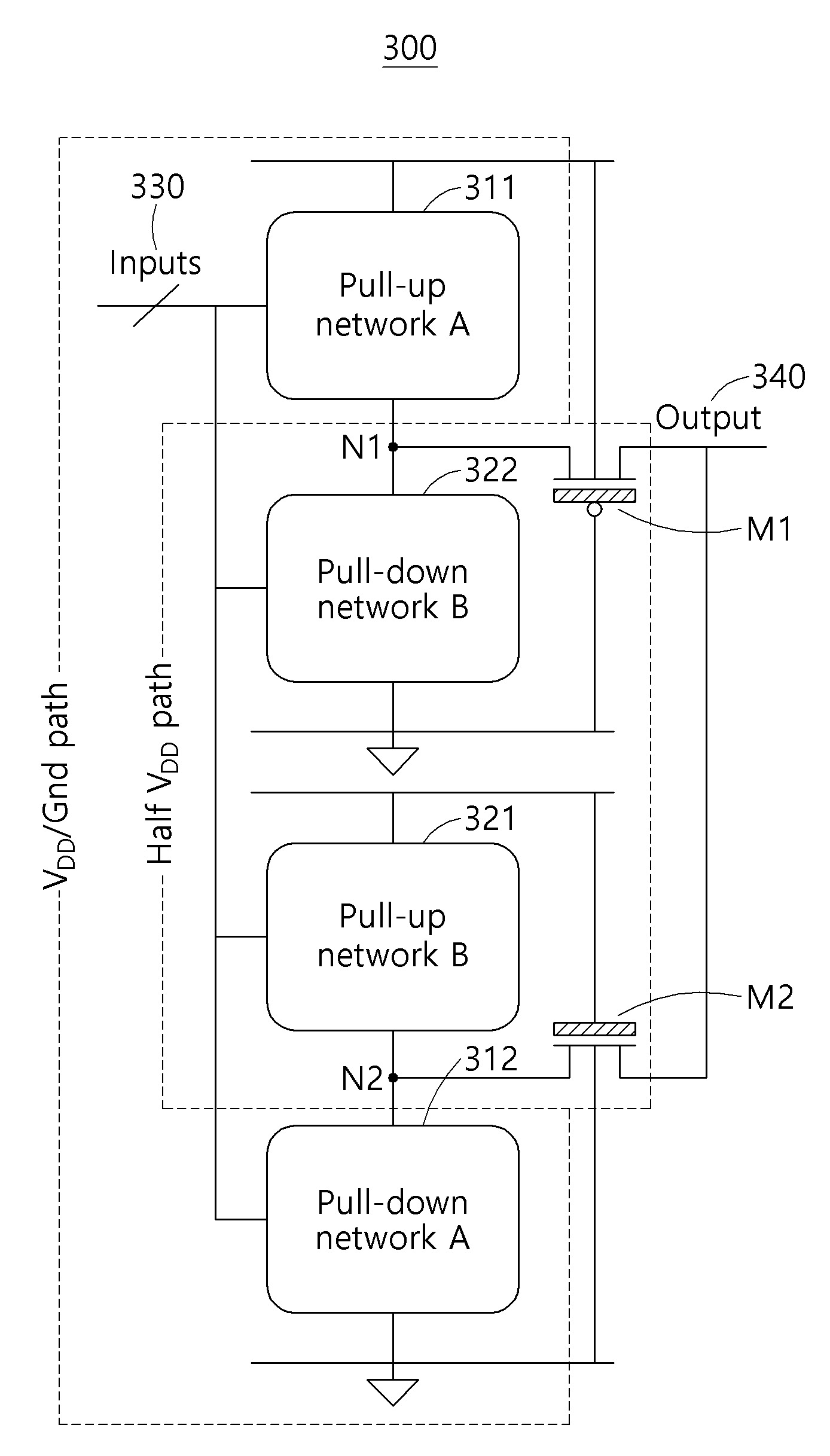

| 1 | 제1 풀업 회로가 턴온되면 드레인 전압을 제1 트랜지스터를 통해 출력하고, 제1 풀다운 회로가 턴온되면 접지 전압을 제2 트랜지스터를 통해 출력하는 드레인-접지 경로; 제2 풀업 회로 및 제2 풀다운 회로가 둘 다 턴온되면 상기 제1 트랜지스터 및 상기 제2 트랜지스터를 통해 하프 드레인 전압을 출력하는 하프 드레인 경로를 포함하고,상기 제1 트랜지스터는,상기 제1 풀업 회로 및 상기 제2 풀다운 회로 사이의 제1 노드를 출력 단자에 연결하며,상기 제2 트랜지스터는,상기 제2 풀업 회로 및 상기 제1 풀다운 회로 사이의 제2 노드를 상기 출력 단자에 연결하는,스태틱 삼진 게이트. |

| 2 | 제1항에 있어서,상기 제1 풀업 회로는,상기 제2 풀다운 회로, 상기 드레인 전압을 공급하는 드레인 전원, 및 상기 제1 트랜지스터를 연결하고,상기 제1 풀다운 회로는,상기 제2 풀업 회로, 상기 접지 전압을 공급하는 접지, 및 상기 제2 트랜지스터를 연결하는,스태틱 삼진 게이트. |

| 3 | 제1항에 있어서,상기 제2 풀업 회로는,상기 제1 풀다운 회로, 상기 드레인 전압을 공급하는 드레인 전원, 및 상기 제2 트랜지스터를 연결하고,상기 제2 풀다운 회로는,상기 제1 풀업 회로, 상기 접지 전압을 공급하는 접지, 및 상기 제1 트랜지스터를 연결하는,스태틱 삼진 게이트. |

| 4 | 제1항에 있어서,상기 제1 풀업 회로 및 상기 제2 풀업 회로는, 상기 제1 트랜지스터와 같은 도핑 타입의 트랜지스터를 포함하고,상기 제1 풀다운 회로 및 상기 제2 풀다운 회로는, 상기 제2 트랜지스터와 같은 도핑 타입의 트랜지스터를 포함하며,상기 제1 트랜지스터 및 상기 제2 트랜지스터는 서로 반대되는 도핑 타입을 가지는,스태틱 삼진 게이트. |

| 5 | 제1항에 있어서,상기 제1 트랜지스터는 p타입 트랜지스터이고, 상기 제2 트랜지스터는 n타입 트랜지스터인,스태틱 삼진 게이트. |

| 6 | 제1항에 있어서,상기 제1 트랜지스터는 및 상기 제2 트랜지스터는 단일 벽 탄소나노튜브 전계효과 트랜지스터(CNTFET)인,스태틱 삼진 게이트. |

| 7 | 제1항에 있어서,상기 제1 풀업 회로, 상기 제1 풀다운 회로, 상기 제2 풀업 회로, 및 상기 제2 풀다운 회로는,하프 드레인 전압 미만인 제1 문턱 전압(threshold voltage)을 갖는 트랜지스터 및 하프 드레인 전압 이상인 제2 문턱 전압을 갖는 트랜지스터로 구성되며,상기 제1 트랜지스터 및 상기 제2 트랜지스터는,상기 제1 문턱 전압과 상기 제2 문턱 전압 사이의 제3 문턱 전압을 갖는 트랜지스터인,스태틱 삼진 게이트. |

| 8 | 제1항에 있어서,상기 제2 풀업 회로 및 상기 제2 풀다운 회로가 둘 다 턴온되어 상기 출력 단자에서 하프 드레인 전압을 출력하는 경우, 상기 제1 트랜지스터 및 상기 제2 트랜지스터는 둘 다 턴오프되어 하프 드레인 전압의 출력을 유지하는,스태틱 삼진 게이트. |

| 9 | 제1항에 있어서,상기 출력 단자에서 출력되는 출력 전압이 드레인 전압에서 하프 드레인 전압으로 감소하는 경우, 상기 제2 풀다운 회로가 턴온되어 상기 제1 노드의 전압이 드레인 전압에서 접지 전압으로 전이되고, 상기 제1 노드와 연결된 상기 제1 트랜지스터는 상기 출력 전압을 하프 드레인 전압에서 유지시키는,스태틱 삼진 게이트. |

| 10 | 제1항에 있어서,상기 출력 단자에서 출력되는 출력 전압이 접지 전압에서 하프 드레인 전압으로 증가하는 경우, 상기 제2 풀업 회로가 턴온되어 상기 제2 노드의 전압이 접지 전압에서 드레인 전압으로 전이되고, 상기 제2 노드와 연결된 상기 제2 트랜지스터는 상기 출력 전압을 하프 드레인 전압에서 유지시키는,스태틱 삼진 게이트. |

| 11 | 제9항에 있어서,상기 출력 전압이 드레인 전압에서 하프 드레인 전압으로 감소하는 경우, 상기 제1 노드의 전압이 문턱 전압 이하가 되는 경우 상기 제1 트랜지스터가 오프되는,스태틱 삼진 게이트. |

| 12 | 제10항에 있어서,상기 출력 전압이 접지 전압에서 하프 드레인 전압으로 증가하는 경우, 상기 제2 노드의 전압이 드레인 전압에서 문턱 전압을 감산한 전압 이상이 되는 경우 상기 제2 트랜지스터가 턴오프되는,스태틱 삼진 게이트. |

| 13 | 제1항에 있어서,상기 제1 트랜지스터의 바디(body)는 드레인 전압을 공급하는 드레인 전원과 연결되고, 상기 제2 트랜지스터의 바디는 접지 전압을 공급하는 접지와 연결되는,스태틱 삼진 게이트. |

| 14 | 제1항에 있어서,상기 스태틱 삼진 게이트는,상기 출력 단자에 연결되는 외부 전원을 더 포함하고,상기 외부 전원에 의하여 상기 출력 단자에서 출력되는 출력 전압이 감소하는 경우에 응답하여, 상기 제1 트랜지스터에 흐르는 제1 전류가 감소하고, 상기 제2 트랜지스터에 흐르는 제2 전류가 증가하며,상기 외부 전원에 의하여 상기 출력 전압이 증가하는 경우에 응답하여, 상기 제1 트랜지스터에 흐르는 상기 제1 전류가 증가하고, 상기 제2 트랜지스터에 흐르는 상기 제2 전류가 감소하는,스태틱 삼진 게이트. |

| 15 | 삼진 논리에 대응하는 진리표를 이용하여 회로에 대한 스위칭 테이블을 생성하는 단계;상기 스위칭 테이블을 곱의 합(Sum Of Product) 표현으로 변환하는 단계;곱의 합 표현으로 변환되는 상기 스위칭 테이블을 퀸맥클러스키(Quine-McCluskey) 알고리즘을 이용하여 최소화하는 단계; 및상기 스위칭 테이블에 기초하여 주어진 신호(given signal)에 대응하는 트랜지스터를 선택하여 제어하는 단계;를 포함하고,상기 회로는,턴온될 시 드레인 전압을 출력하는 제1 풀업 회로;턴온될 시 접지 전압을 출력하는 제1 풀다운 회로;제2 풀다운 회로와 함께 턴온될 시 하프 드레인 전압을 출력하는 제2 풀업 회로;상기 제1 풀업 회로 및 상기 제2 풀다운 회로 사이의 제1 노드를 출력 단자에 연결하는 제1 트랜지스터; 및상기 제2 풀업 회로 및 상기 제1 풀다운 회로 사이의 제2 노드를 상기 출력 단자에 연결하는 제2 트랜지스터를 포함하는 스태틱 삼진 게이트를 설계하는 방법. |