| 번호 | 청구항 |

|---|---|

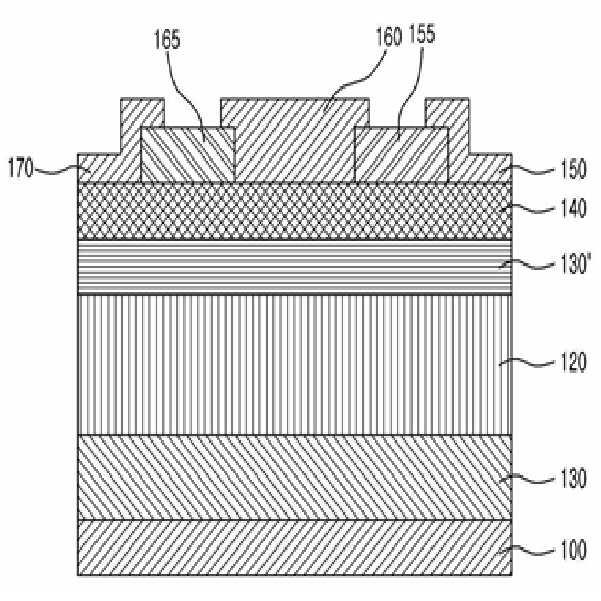

| 1 | 게이트 전극;상기 게이트 전극 상에 형성된 제1 전도성 삽입층;상기 제1 전도성 삽입층 상에 형성된 바이폴라리티(bi-polarity) 특성의 스위처블 재료층;상기 스위처블 재료층 상에 형성된 제2 전도성 삽입층;상기 제2 전도성 삽입층 상에 형성된 제1 유전체층;상기 제1 유전체층 상에 형성된 제1 반도체층을 가지는 제1 트랜지스터; 및상기 제1 반도체층과 전기적으로 연결된 제2 반도체층을 가지는 제2 트랜지스터를 포함하고, 상기 제1 트랜지스터 및 상기 제2 트랜지스터를 포함하는 노드(node)의 동작은 스위처블 재료층의 분극 상태로 제어되는 가중치 노드인 것을 특징으로 하는 가중치 소자. |

| 2 | 제1항에 있어서,상기 스위처블 재료층은 멀티페로익(multiferroic) 물질이고, HoMnO3, TbMnO3, BuMnO3, ErMnO3. YbMnO3 BiFeO3, BaNiF4, ZnCr2Se4 및 LiCu2O2로 이루어진 군에서 선택된 적어도 어느 하나인 것을 특징으로 하는 가중치 소자. |

| 3 | 제1항에 있어서,상기 제1 전도성 삽입층 및 상기 제2 전도성 삽입층은 SrRuOx, IrOx, RuOx, MnOx, NiOx, CoMnOx 및 La1-xSrxCoO3로 이루어진 전도성 산화물군에서 선택된 적어도 어느 하나인 것을 특징으로 하는 가중치 소자. |

| 4 | 제1항에 있어서, 상기 스위처블 재료층은 강유전체 물질이고, Pb(ZrxTi1-x)O3(0≤x≤1), SrBiTaO9, Bi4Ti3O12, BaTiO3, HfOx, PbTiO3, HfZrOx 및 Poly(methyl methacrylate)로 이루어진 군에서 선택된 적어도 어느 하나인 것을 특징으로 하는 가중치 소자. |

| 5 | 제1항에 있어서,상기 제1유전체층은 SiO2, HfO2, Al2O3, TiO2, ZrO2, SiNx, Si3N4, Ta2O5 및 SrTiO3로 이루어진 군에서 선택된 적어도 어느 하나인 것을 특징으로 하는 가중치 소자. |

| 6 | 제1항에 있어서, 상기 제1 트랜지스터는,n타입 전이금속 디칼코게니드(Transition Metal Dichalcogenide, TMD)인 제1 반도체층;상기 제1 반도체층과 전기적으로 연결된 제1 소스 전극; 및상기 제1 반도체층과 전기적으로 연결되고, 상기 제1 소스 전극과 대향하는 드레인 전극을 포함하는 것을 특징으로 하는 가중치 소자. |

| 7 | 제1항에 있어서, 상기 제2 트랜지스터는,p타입 전이금속 디칼코게니드(Transition Metal Dichalcogenide, TMD)인 제2 반도체층;상기 제2 반도체층과 전기적으로 연결된 제2 소스 전극; 및상기 제2 반도체층과 전기적으로 연결되고, 상기 제2 소스 전극과 대향하는 드레인 전극을 포함하는 것을 특징으로 하는 가중치 소자. |

| 8 | 제6항 또는 제7항에 있어서, 상기 전이금속 디칼코게니드는 n 타입 또는 p 타입이고, ZrSe2, TaSe2, TaS2, NbSe2, WSe2, MoTe2, MoSe2, MoS2, SnSe2 및 SnS2로 이루어진 군에서 선택된 적어도 어느 하나인 것을 특징으로 하며, 상기 군들 중 어느 하나에 도핑(doping)을 하여 n 타입 또는 p 타입으로 제작하는 것을 특징으로 하는 가중치 소자. |

| 9 | 제1항에 있어서,상기 제1 트랜지스터 및 상기 제2 트랜지스터는 TFT인 것을 특징으로 하는 가중치 소자. |

| 10 | 제1항에 있어서,상기 제1 반도체층은 n 타입 전이금속 다이칼코겐나이드(Transition Metal Dichalcogenide, TMD)로 형성되고,상기 제2 반도체층은 p 타입 전이금속 다이칼코겐나이드(Transition Metal Dichalcogenide, TMD)로 형성되는 것을 특징으로 하는 가중치 소자. |

| 11 | 제6항에 있어서, 상기 드레인 전극과 컨택 전극을 통해 전기적으로 연결되어 있는 선택 트랜지스터(select transistor)를 포함하는 것을 특징으로 하는 가중치 소자. |

| 12 | 제11항에 있어서, 상기 선택 트랜지스터는, 게이트(gate) 전극;상기 게이트 전극 상을 덮는 형상의 제2 유전체층;상기 제2 유전체층 상에 형성된 제3 반도체층;상기 제3 반도체층과 전기적으로 연결된 제3 소스 전극;상기 제3 반도체층과 전기적으로 연결되고, 상기 제3소스 전극과 대향하는 제2 드레인 전극을 포함하는 것을 특징으로 하는 가중치 소자. |

| 13 | 제12항에 있어서,상기 제3 반도체층은 전이금속 디칼코게니드, 실리콘 박막, 비정질 실리콘 및 산화물 반도체 박막으로 이루어진 군에서 선택된 어느 하나인 것을 특징으로 하는 가중치 소자. |

| 14 | 제11항에 있어서,상기 가중치 노드와 상기 선택 트랜지스터를 일대일로 연결하고, 상기 가중치 노드가 평면상으로 배열된 구조의 배열층과 상기 선택 트랜지스터가 평면상으로 배열된 구조의 배열층이 번갈아 적층된 구조로 형성된 것을 특징으로 하는 가중치 소자. |

| 15 | 제11항에 있어서,적층으로 상기 가중치소자를 제작하고, 상기 선택 트랜지스터는 TFT인 것을 특징으로 하는 가중치 소자. |

| 16 | 기판 상에 형성된 게이트 전극, 상기 게이트 전극 상에 형성된 제1 전도성 삽입층, 상기 제1 전도성 삽입층 상에 형성된 바이폴라리티(bi-polarity) 특성의 스위처블 재료층, 상기 스위처블 재료층 상에 형성된 제2 전도성 삽입층, 상기 제2 전도성 삽입층 상에 형성된 제1 유전체층, 상기 제1 유전체층 상에 형성된 제1 반도체층을 가지는 제1 트랜지스터 및 상기 제1 반도체층과 전기적으로 연결된 제2 반도체층을 가지는 제2 트랜지스터를 포함하는 가중치 소자에 있어서, 상기 게이트 전극에 게이트 전압(Vp)을 인가하고, 상기 제1 유전체층과 상기 스위처블 재료층에 부분적으로 전압을 인가하는 단계; 및상기 게이트 전압(Vp)와 상기 제1 유전체층 전압(Vox)의 차이값인 스위처블 재료층에 인가되는 전압(VF)이 상기 스위처블 재료층의 보자 전압(coercive voltage)보다 크도록 하되, 잔류 분극량이 균일하게 변하도록 조정하는 단계를 포함하는 가중치 소자의 동작 방법. |

| 17 | 제16항에 있어서,상기 제1 트랜지스터 및 상기 제2 트랜지스터가 컨택 전극을 통해 전기적으로 연결된 선택 트랜지스터를 포함하는 상기 가중치 소자에 있어서,상기 게이트 전극이 접지되어 있고, 상기 선택 트랜지스터를 통해 상기 컨택 전극에 전압(Vb)을 인가하는 단계; 및상기 컨택 전극에 인가된 전압(Vb)과 상기 제1 유전체층에 인가된 전압(Vox)의 차이값인 스위처블 재료층에 인가되는 전압(VF)이 상기 스위처블 재료층의 보자 전압(coercive voltage) 보다 크도록 하되, 잔류분극량이 균일하게 변하도록 조정하는 역단계를 포함하는 가중치 소자의 동작 방법. |

| 18 | 제16항에 있어서,상기 가중치 소자에 있어서,잔류 분극량을 균일하게 제어함으로써 선형성(linearity)를 얻기 위하여 인가 펄스(pulse)의 전압, 펄스폭(pulse width) 및 펄스 전류(pulse current)를 제어하는 단계를 포함하는 가중치 소자의 동작 방법. |

| 19 | 제18항에 있어서,상기 가중치 소자에 있어서,선형성(linearity) 제어를 네거티브 폴라리티(negative polarity 또는 polarization)에서 포지티브 폴라리티(positive polarity 또는 polarization)까지 선택 트랜지스터를 이용하여 다단계로 수행하는 단계를 포함하는 가중치 소자의 동작 방법. |

| 20 | 제16항에 있어서,상기 가중치 소자에 있어서,스위처블 재료층의 표면 상태를 상기 제1 트랜지스터와 상기 제2 트랜지스터로 동시에 검출하여 포지티브 가중치(positive weights)와 네거티브 가중치(negative weights)에 의한 전류 방향과 크기를 동시에 구별하는 단계를 포함하는 가중치 소자의 동작 방법. |

| 21 | 기판 상에 형성된 게이트 전극, 상기 게이트 전극 상에 형성된 제1 전도성 삽입층, 상기 제1 전도성 삽입층 상에 형성된 바이폴라리티(bi-polarity) 특성의 스위처블 재료층, 상기 스위처블 재료층 상에 형성된 제2 전도성 삽입층, 상기 제2 전도성 삽입층 상에 형성된 제1 유전체층, 상기 제1 유전체층 상에 형성된 제1 반도체층을 가지는 제1 트랜지스터 및 상기 제1 반도체층과 전기적으로 연결된 제2 반도체층을 가지는 제2 트랜지스터를 포함하는 가중치 소자에 있어서,특정 펄스폭을 가진 특정 전압 펄스를 상기 게이트 전극에 인가하는 단계;상기 스위처블 재료층이 최대 네거티브(maximum negative) 잔류 분극량을 갖도록 상기 특정 전압 펄스를 네거티브 리셋 펄스(negative reset pulse)로 상기 게이트 전극에 인가하는 단계; 상기 스위처블 재료층이 특정 포지티브(positive) 잔류 분극량을 갖도록 상기 특정 전압 펄스를 포지티브 펄스(positive pulse)로 상기 게이트 전극에 인가하는 단계; 상기 네거티브 리셋 펄스 및 상기 포지티브 펄스의 피크값을 변경하여 상기 게이트 전극에 인가하는 단계; 및상기 가중치 소자에 특정 포지티브 가중치가 변경되는 단계를 포함하는 가중치 소자의 동작 방법. |

| 22 | 기판 상에 형성된 게이트 전극, 상기 게이트 전극 상에 형성된 제1 전도성 삽입층, 상기 제1 전도성 삽입층 상에 형성된 바이폴라리티(bi-polarity) 특성의 스위처블 재료층, 상기 스위처블 재료층 상에 형성된 제2 전도성 삽입층, 상기 제2 전도성 삽입층 상에 형성된 제1 유전체층, 상기 제1 유전체층 상에 형성된 제1 반도체층을 가지는 제1 트랜지스터 및 상기 제1 반도체층과 전기적으로 연결된 제2 반도체층을 가지는 제2 트랜지스터를 포함하는 가중치 소자에 있어서,특정 펄스폭을 가진 특정 전압 펄스를 상기 게이트 전극에 인가하는 단계;상기 스위처블 재료층이 최대 포지티브(maximum positive) 잔류 분극량을 갖도록 상기 특정 전압 펄스를 포지티브 리셋 펄스(positive reset pulse)로 상기 게이트 전극에 인가하는 단계; 상기 스위처블 재료층이 특정 네거티브(negative) 잔류 분극량을 갖도록 상기 특정 전압 펄스를 네거티브 펄스(negative pulse)로 상기 게이트 전극에 인가하는 단계;상기 포지티브 리셋 펄스 및 상기 네거티브 펄스의 피크값을 변경하여 상기 게이트 전극에 인가하는 단계; 및상기 가중치 소자에 특정 네거티브 가중치가 변경되는 단계를 포함하는 가중치 소자의 동작 방법. |