| 번호 | 청구항 |

|---|---|

| 12 | 제11항에 있어서,상기 패시베이션막은 실리콘 산화막인, In계 복합 산화물 반도체층 결정화 방법. |

| 1 | 기판 상에 In계 복합 산화물 반도체층(Indium-based composite oxide semiconductor layer)을 형성하고, 상기 기판을 제1 열처리하여 상기 In계 복합 산화물 반도체층 내의 금속-산소 결합을 파괴하되, 비정질 상태는 유지하도록 하는 단계;상기 In계 복합 산화물 반도체층의 양측 단부들에 In계 산화물 도전체 패턴들을 형성하고, 상기 기판을 제2 열처리하여 상기 In계 산화물 도전체 패턴들을 빅스비아이트(Bixbyite) 결정을 갖도록 결정화하는 단계; 및 상기 기판을 제3 열처리하여 상기 결정화된 In계 산화물 도전체 패턴들에 의해 상기 In계 복합 산화물 반도체층을 유도결정화하여, 상기 In계 복합 산화물 반도체층을 [222] 방향으로 우선 배향되도록 결정화하는 단계를 포함하는, In계 복합 산화물 반도체층 결정화 방법. |

| 2 | 제1항에 있어서,상기 In계 복합 산화물 반도체층은 인듐에 더하여 다른 금속 원소를 포함하는 삼성분계 산화물(ternary oxide) 또는 사성분계 산화물(quaternary oxide)인, In계 복합 산화물 반도체층 결정화 방법. |

| 3 | 제2항에 있어서,상기 삼성분계 산화물은 In-Ga-O(IGO) 또는 In-Zn-O(IZO)인, In계 복합 산화물 반도체층 결정화 방법. |

| 4 | 제2항에 있어서,상기 사성분계 산화물은 In-Ga-Zn-O(IGZO) 또는 In-Zn-Sn-O(IZTO)인, In계 복합 산화물 반도체층 결정화 방법. |

| 5 | 제1항에 있어서,상기 제1 열처리는 300 초과 500℃ 미만의 온도로 수행되는, In계 복합 산화물 반도체층 결정화 방법. |

| 6 | 제5항에 있어서,상기 제1 열처리는 350 내지 450℃의 온도로 수행되는, In계 복합 산화물 반도체층 결정화 방법. |

| 7 | 제1항에 있어서,상기 제1 열처리는 산소 분위기에서 0.5 내지 2 시간 동안 수행되는, In계 복합 산화물 반도체층 결정화 방법. |

| 8 | 제1항에 있어서,상기 In계 산화물 도전체 패턴들은 In-Sn-O(ITO) 또는 In-Zn-O(IZO)인, In계 복합 산화물 반도체층 결정화 방법. |

| 9 | 제1항에 있어서,상기 제2 열처리는 180 내지 220℃의 온도로 수행되는, In계 복합 산화물 반도체층 결정화 방법. |

| 10 | 제1항에 있어서,상기 제2 열처리 후에도 상기 In계 복합 산화물 반도체층은 비정질 상태를 유지하는, In계 복합 산화물 반도체층 결정화 방법. |

| 11 | 제1항에 있어서,상기 기판을 제3 열처리하기 전에, 상기 결정화된 In계 산화물 도전체 패턴들을 덮는 패시베이션막을 형성하는 단계를 더 포함하는, In계 복합 산화물 반도체층 결정화 방법. |

| 13 | 제1항에 있어서,상기 결정화된 In계 복합 산화물 반도체층은 XRD (X-ray diffraction) 스펙트럼에서 (400) 피크 강도에 대한 (222) 피크 강도의 비가 6 내지 8인, In계 복합 산화물 반도체층 결정화 방법. |

| 14 | 제1항에 있어서,상기 결정화된 In계 산화물 도전체 패턴과 이에 의해 유도결정화된 상기 In계 복합 산화물 반도체층은 격자 부정합도(lattice mismatch degree)가 2.5% 미만인, In계 복합 산화물 반도체층 결정화 방법. |

| 15 | 제1항에 있어서,상기 결정화된 In계 복합 산화물 반도체층은 상기 In계 산화물 도전체 패턴들에 접하는 양측단부로부터 중심부 방향으로 결정화도가 낮아지는, In계 복합 산화물 반도체층 결정화 방법. |

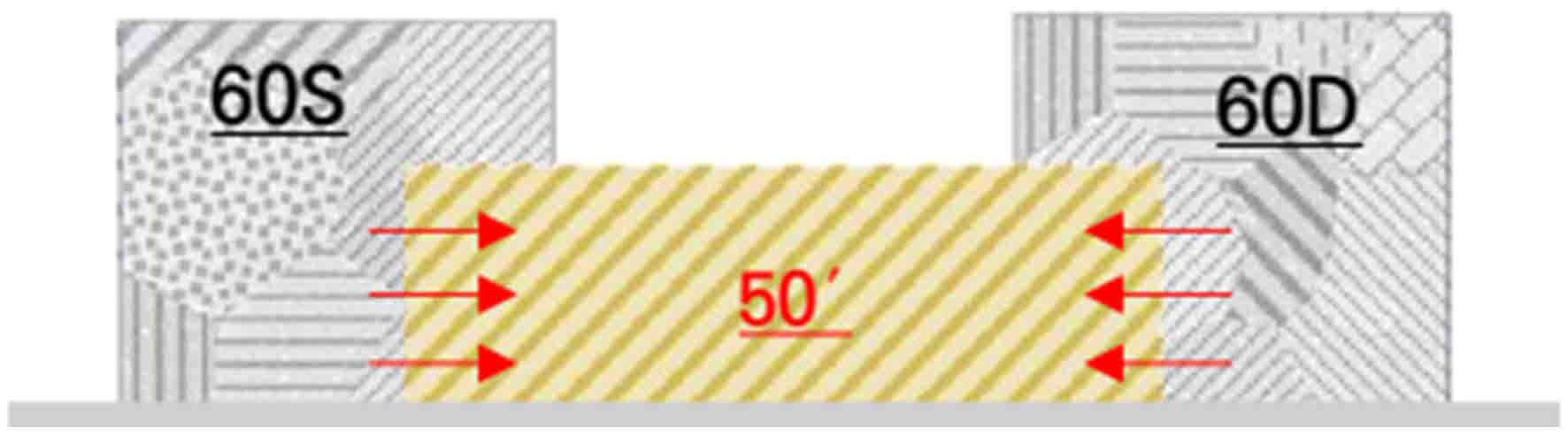

| 16 | 제1항에 있어서,상기 결정화된 In계 복합 산화물 반도체층은 상기 In계 산화물 도전체 패턴들 사이에 노출된 영역의 외곽부분이 먼저 결정화되고 중심부는 비정질 상태로 남아 있는, In계 복합 산화물 반도체층 결정화 방법. |

| 17 | 기판 상에 게이트 전극을 형성하고, 상기 게이트 전극 상에 게이트 절연막을 형성하는 단계;상기 게이트 절연막 상에 In계 복합 산화물 반도체층(Indium-based composite oxide semiconductor layer)을 형성하고, 상기 기판을 제1 열처리하여 상기 In계 복합 산화물 반도체층 내의 금속-산소 결합을 파괴하되, 비정질 상태는 유지하도록 하는 단계;상기 In계 복합 산화물 반도체층의 양측 단부들에 In계 산화물 도전체 패턴들을 형성하고, 상기 기판을 제2 열처리하여 상기 In계 산화물 도전체 패턴들을 빅스비아이트(Bixbyite) 결정을 갖도록 결정화하는 단계; 및상기 기판을 제3 열처리하여 상기 결정화된 In계 산화물 도전체 패턴들에 의해 상기 In계 복합 산화물 반도체층을 유도결정화하여, 상기 In계 복합 산화물 반도체층을 [222] 방향으로 우선 배향되도록 결정화하는 단계를 포함하는, 박막트랜지스터 제조방법. |

| 18 | 제17항에 있어서,상기 결정화된 In계 산화물 도전체 패턴들은 소오스/드레인 전극들인, 박막트랜지스터 제조방법. |

| 19 | 삭제 |

| 20 | 게이트 전극;상기 게이트 전극과 중첩되고 빅스비아이트(Bixbyite) 결정을 구비하고 (222)면으로 우선 배향된 In계 복합 산화물 반도체층;상기 게이트 전극과 상기 In계 복합 산화물 반도체층 사이에 배치된 게이트 절연막; 및상기 In계 복합 산화물 반도체층의 양측 단부들에 각각 전기적으로 접속하는 소오스 및 드레인 전극들을 포함하고,상기 In계 복합 산화물 반도체층은 양측 단부로부터 중심부 방향으로 결정화도가 낮아지는, 박막트랜지스터. |

| 21 | 게이트 전극;상기 게이트 전극과 중첩되고 빅스비아이트(Bixbyite) 결정을 구비하고 (222)면으로 우선 배향된 In계 복합 산화물 반도체층;상기 게이트 전극과 상기 In계 복합 산화물 반도체층 사이에 배치된 게이트 절연막; 및상기 In계 복합 산화물 반도체층의 양측 단부들에 각각 전기적으로 접속하는 소오스 및 드레인 전극들을 포함하고,상기 In계 복합 산화물 반도체층은 상기 소오스 및 드레인 전극들 사이의 채널 영역의 외곽부분이 결정화되고 중심부는 비정질 상태로 남아 있는, 박막트랜지스터. |

| 22 | 게이트 전극;상기 게이트 전극과 중첩되고 빅스비아이트(Bixbyite) 결정을 구비하고 (222)면으로 우선 배향된 In계 복합 산화물 반도체층;상기 게이트 전극과 상기 In계 복합 산화물 반도체층 사이에 배치된 게이트 절연막; 및상기 In계 복합 산화물 반도체층의 양측 단부들에 각각 전기적으로 접속하는 소오스 및 드레인 전극들을 포함하고,상기 In계 복합 산화물 반도체층은 XRD (X-ray diffraction) 스펙트럼에서 (400) 피크 강도에 대한 (222) 피크 강도의 비가 6 내지 8인, 박막트랜지스터. |

| 23 | 게이트 전극;상기 게이트 전극과 중첩되고 빅스비아이트(Bixbyite) 결정을 구비하고 (222)면으로 우선 배향된 In계 복합 산화물 반도체층;상기 게이트 전극과 상기 In계 복합 산화물 반도체층 사이에 배치된 게이트 절연막; 및상기 In계 복합 산화물 반도체층의 양측 단부들에 각각 전기적으로 접속하는 소오스 및 드레인 전극들을 포함하고,상기 소오스/드레인 전극들은 빅스비아이트(Bixbyite) 결정을 갖도록 결정화된 In계 산화물 도전체 패턴들인, 박막트랜지스터. |

| 24 | 제23항에 있어서,상기 결정화된 In계 산화물 도전체 패턴들에 의해 상기 In계 복합 산화물 반도체층은 유도결정화된, 박막트랜지스터. |

| 25 | 제24항에 있어서,상기 결정화된 In계 산화물 도전체 패턴과 이에 의해 유도결정화된 상기 In계 복합 산화물 반도체층은 격자 부정합도(lattice mismatch degree)가 2.5% 미만인, 박막트랜지스터. |