| 번호 | 청구항 |

|---|---|

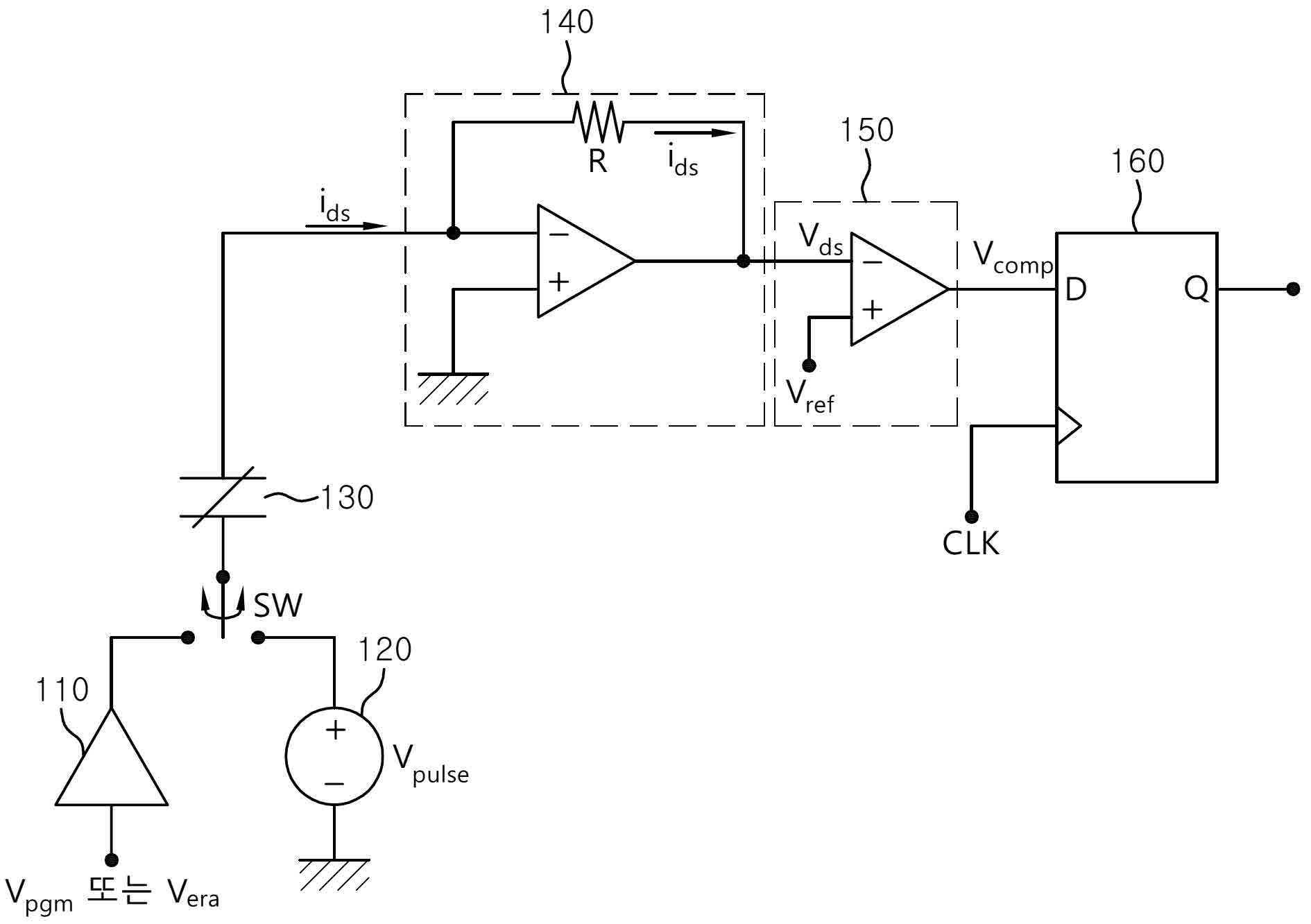

| 1 | 프로그램 전압 또는 소거 전압을 공급하는 초기화 전원;펄스 전압을 공급하는 펄스원;상기 초기화 전원 및 상기 펄스원에 상보적으로 연결되며, 프로그램 동작에 의해 문턱 전압이 랜덤하게 분포되며, 상기 펄스 전압의 공급에 의해 발생되는 불규칙한 방전 전류가 형성되는 멤커패시터;상기 멤커패시터에서 형성된 상기 방전 전류를 전압으로 변환하여 변환 전압을 형성하는 전류-전압 변환기;상기 전류-전압 변환기의 상기 변환 전압과 기준 전압을 비교하여 비교 전압을 형성하는 비교기; 및클럭 신호에 동기화되어 랜덤하게 변하는 비교 전압을 샘플링하여 디지털 신호로 출력하는 D-플립플롭을 포함하는 난수 발생기. |

| 2 | 제1항에 있어서, 상기 멤커패시터는 p형 실리콘 기판 상에 SiO2층, HfO2층, Al2O3층 및 TiN층이 순차 적층된 TAHOS 구조를 가지는 것을 특징으로 하는 난수 발생기. |

| 3 | 제1항에 있어서, 상기 멤커패시터는p형 실리콘 기판;상기 p형 실리콘 기판 상에 형성된 터널 절연막;상기 터널 절연막 상에 형성된 전하 트랩층; 상기 전하 트랩층 상에 형성된 제어 절연막; 및상기 제어 절연막 상에 형성된 게이트 전극을 포함하고, 상기 전하 트랩층에 전자가 포획됨에 의해 프로그램 동작이 수행되고, 상기 전하 트랩층에 포획된 전자가 상기 p형 실리콘 기판으로 이동함에 의해 소거 동작이 수행되는 것을 특징으로 하는 난수 발생기. |

| 4 | 제3항에 있어서, 상기 전류-전압 변환기는 OP-AMP와 상기 OP-AMP의 음의 입력단과 출력단 사이에 배치된 피드백 저항을 포함하고, 상기 p형 반도체 기판은 상기 OP-AMP의 상기 음의 입력단에 연결되고, 상기 게이트 전극은 상기 초기화 전원 또는 펄스원에 선택적으로 연결되는 것을 특징으로 하는 난수 발생기. |

| 5 | 제4항에 있어서, 상기 펄스원이 공급하는 펄스 전압은 상기 초기화 전원에 의해 상기 소거 동작 및 프로그램 동작이 수행된 이후에 인가되는 것을 특징으로 하는 난수 발생기. |

| 6 | 제5항에 있어서, 상기 프로그램 동작에 따른 상기 멤커패시터의 문턱 전압의 평균치는 상기 펄스 전압의 하이 레벨인 충전 전압과 로우 레벨인 방전 전압 사이에 배치되는 것을 특징으로 하는 난수 발생기. |

| 7 | 제5항에 있어서, 상기 프로그램 동작에 의해 게이트 전압이 문턱 전압 미만이면 상기 멤커패시터는 표면 축적에 의해 상기 게이트 전압이 음의 값에서 0V로 향할수록 커패시턴스가 감소하고, 상기 게이트 전압이 문턱 전압 이상이면, 강한 반전에 의해 상기 멤커패시터의 커패시턴스는 0에 도달하는 것을 특징으로 하는 난수 발생기. |

| 8 | 멤커패시터를 이용한 난수 발생 방법에 있어서,상기 멤커패시터에 소거 전압 및 프로그램 전압 순차적으로 인가하여 상기 멤커패시터를 프로그램 상태로 진입시키는 단계;상기 프로그램 상태의 멤커패시터에 펄스 전압을 인가하여 상기 펄스 전압에 따른 방전 전류를 생성하는 단계;상기 방전 전류를 전압의 형태인 변환 전압으로 전환하는 단계;상기 변환 전압을 기준 전압과 비교하여 양의 전원 전압과 음의 전원 전압으로 스윙하는 비교 전압을 생성하는 단계; 및상기 비교 전압을 클럭 신호에 연동하여 상기 클럭 신호의 상승 에서 상기 비교 전압을 샘플링하여 난수를 생성하는 단계를 포함하는 난수 발생 방법. |

| 9 | 제8항에 있어서, 상기 멤커패시터는 p형 실리콘 기판;상기 p형 실리콘 기판 상에 형성된 터널 절연막;상기 터널 절연막 상에 형성된 전하 트랩층; 상기 전하 트랩층 상에 형성된 제어 절연막; 및상기 제어 절연막 상에 형성된 게이트 전극을 포함하고, 상기 전하 트랩층에 전자가 포획됨에 의해 프로그램 동작이 수행되고, 상기 전하 트랩층에 포획된 전자가 상기 p형 실리콘 기판으로 이동함에 의해 소거 동작이 수행되는 것을 특징으로 하는 난수 발생 방법. |

| 10 | 제8항에 있어서, 상기 프로그램 동작에 따른 상기 멤커패시터의 문턱 전압의 평균치는 상기 펄스 전압의 하이 레벨인 충전 전압과 로우 레벨인 방전 전압 사이에 배치되는 것을 특징으로 하는 난수 발생 방법. |

| 11 | 제10항에 있어서, 상기 프로그램 동작에 의해 상기 게이트 전극에 인가되는 게이트 전압이 상기 문턱 전압 미만이면 상기 멤커패시터는 표면 축적에 의해 상기 게이트 전압이 음의 값에서 0V로 향할수록 커패시턴스가 감소하고, 상기 게이트 전압이 상기 문턱 전압 이상이면, 강한 반전에 의해 상기 멤커패시터의 커패시턴스는 0에 도달하는 것을 특징으로 하는 난수 발생 방법. |