| 번호 | 청구항 |

|---|---|

| 7 | 삭제 |

| 8 | 삭제 |

| 9 | 삭제 |

| 10 | 삭제 |

| 11 | 삭제 |

| 12 | 삭제 |

| 1 | 삭제 |

| 2 | 삭제 |

| 3 | 삭제 |

| 4 | 삭제 |

| 5 | 삭제 |

| 6 | 삭제 |

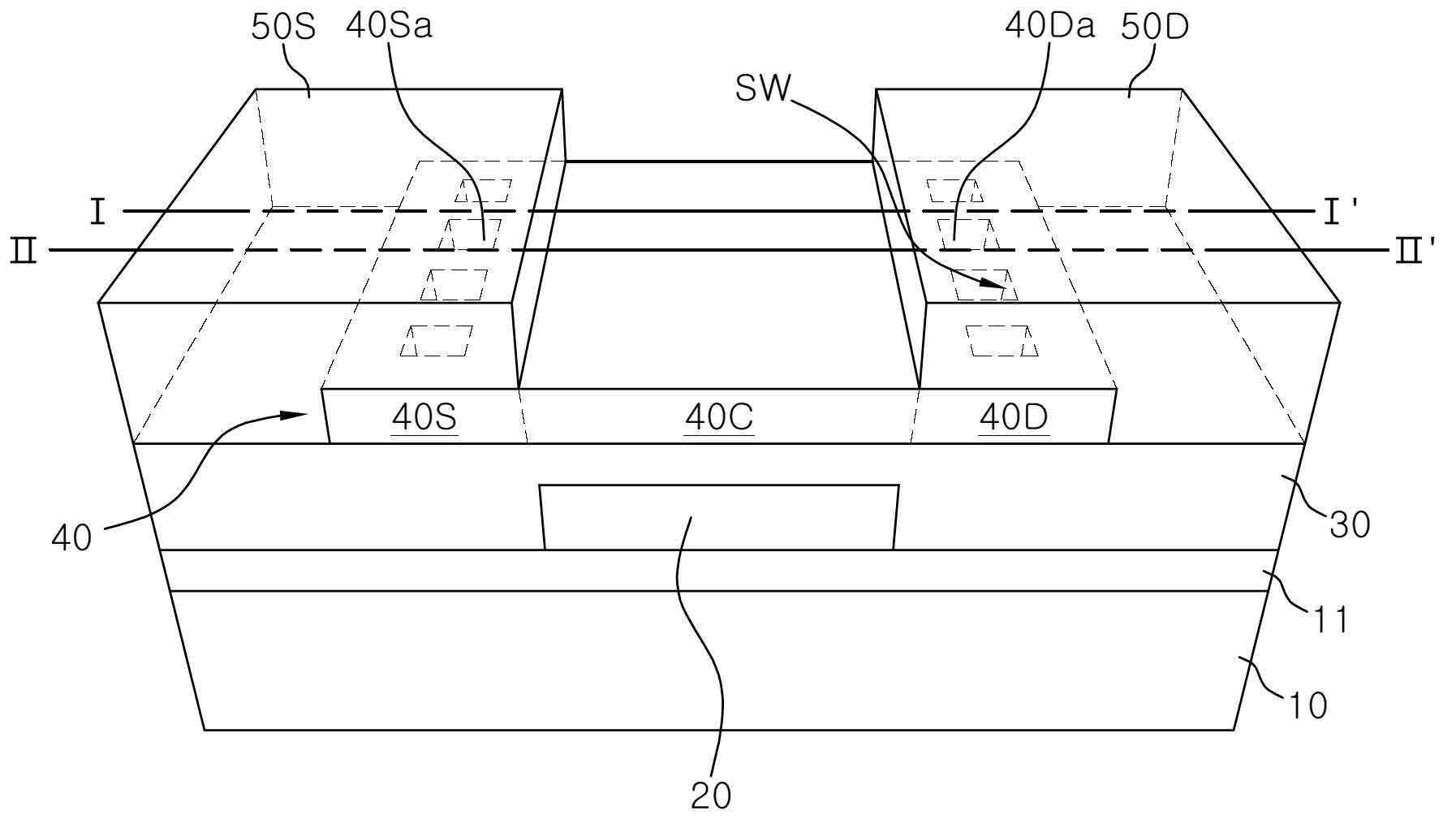

| 13 | 기판 상에 차례로 제1 소오스/드레인 전극, 제1 층간 절연막, 게이트 전극, 및 제2 층간 절연막이 배치되되, 상기 제1 층간 절연막, 상기 게이트 전극, 및 상기 제2 층간 절연막은 상기 제1 층간 절연막, 상기 게이트 전극, 및 상기 제2 층간 절연막을 관통하여 상기 제1 소오스/드레인 전극의 상부 일부분을 노출시키는 트렌치를 구비하고;상기 트렌치의 측벽 상에 게이트 절연막이 배치되되 상기 트렌치의 바닥면에는 상기 게이트 절연막 사이에 상기 제1 소오스/드레인 전극이 노출되고, 상기 게이트 절연막이 배치된 트렌치의 측벽 및 상기 트렌치의 바닥면 상에 배치되어 상기 제1 소오스/드레인 전극에 접속하고 상기 트렌치 주변부로 연장된 반도체 패턴; 상기 트렌치 주변부로 연장된 반도체 패턴 상에 이에 접속하는 제2 소오스/드레인 전극이 배치되어, 상기 반도체 패턴은 상기 제1 소오스/드레인 전극에 중첩된 제1 소오스/드레인 영역, 상기 제2 소오스/드레인 전극에 중첩된 제2 소오스/드레인 영역, 및 상기 소오스/드레인 영역들 사이에 배치된 채널 영역을 구비하고, 상기 제2 소오스/드레인 영역은 상기 반도체 패턴이 리세스된 컨택홀을 구비하고, 상기 제2 소오스/드레인 전극은 상기 컨택홀을 채우고 상기 컨택홀 주변의 반도체 패턴 상으로 연장되고,상기 컨택홀은 상기 제2 소오스/드레인 영역에 3개 이상 형성된 박막트랜지스터. |

| 14 | 삭제 |

| 15 | 청구항 13에 있어서,상기 컨택홀은 직사각형 혹은 둥근 코너를 갖는 사각형인 박막트랜지스터. |

| 16 | 청구항 13에 있어서,상기 컨택홀은 상기 반도체 패턴을 관통하는 형태를 갖는 박막트랜지스터. |

| 17 | 청구항 13에 있어서,상기 컨택홀은 바닥면에 상기 반도체 패턴이 잔존하도록 형성된 박막트랜지스터. |

| 18 | 청구항 13에 있어서,상기 반도체 패턴은 금속 산화물 반도체 패턴인 박막트랜지스터. |