| 번호 | 청구항 |

|---|---|

| 13 | 청구항 7에 있어서, 상기 Zn1-xAlxO층은 0.5 × 1020 cm-3 내지 1.5 × 1020 cm-3 의 전하농도를 갖는 박막트랜지스터 제조방법. |

| 11 | 청구항 7에 있어서, 상기 소오스/드레인 전극들과 상기 저저항층 사이에 배치되고, 상기 저저항층으로부터 산소를 흡수하는 산소 소기막(oxygen scavanging layer)을 더 포함하는 박막트랜지스터 제조방법. |

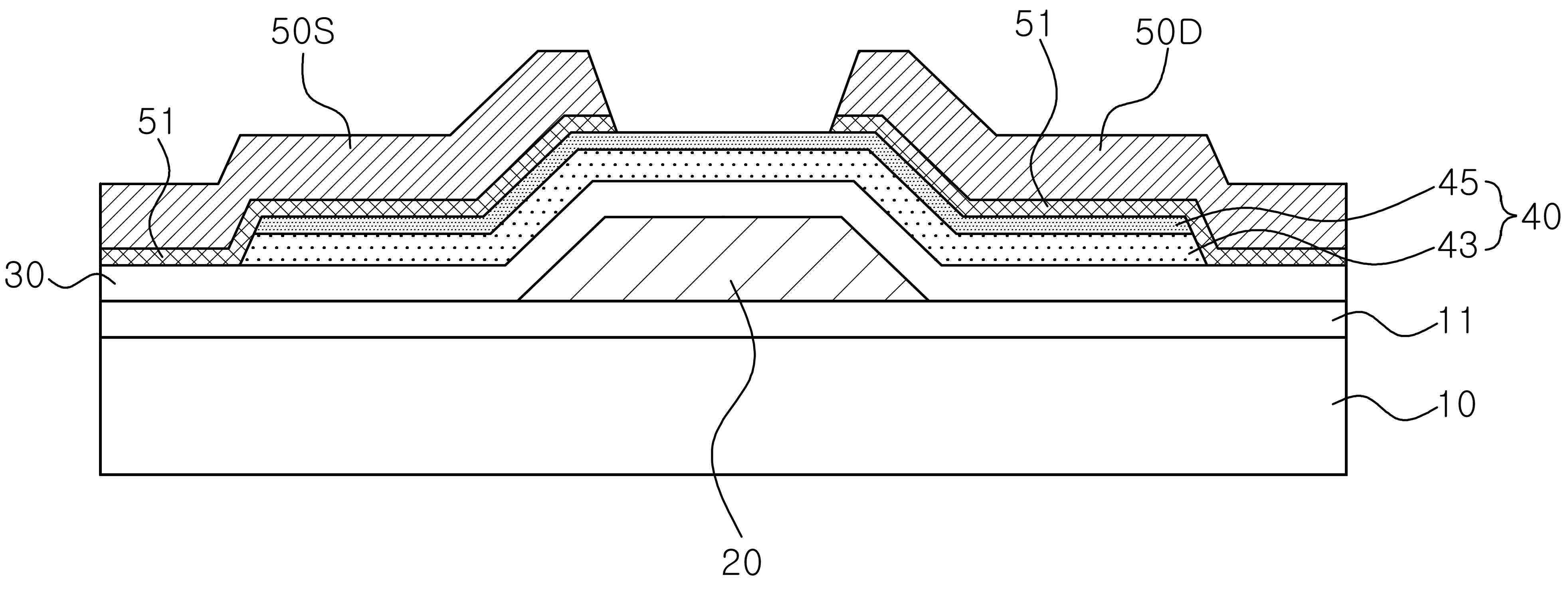

| 1 | 게이트 전극;상기 게이트 전극의 상부, 하부 또는 측면에서 이에 중첩하는 산화물 반도체 채널층;상기 게이트 전극과 상기 산화물 반도체 채널층 사이에 배치된 게이트 절연막;상기 산화물 반도체 채널층의 양측 단부들에 각각 전기적으로 접속하는 소오스/드레인 전극들; 및상기 산화물 반도체 채널층과 상기 소오스/드레인 전극들 사이에 배치된 저저항층을 구비하고,상기 저저항층은 상기 산화물 반도체 채널층 대비 전하농도가 높은 산화물 반도체층이고,상기 저저항층은 상기 산화물 반도체 채널층을 따라 연장되어 상기 소오스/드레인 전극들 사이의 영역에서 상기 게이트 전극과 중첩하도록 배치된 Zn1-xAlxO층(x는 0초과 0.62 이하)이고, 1.7 내지 2.2 nm의 두께를 갖는 박막트랜지스터. |

| 2 | 삭제 |

| 3 | 삭제 |

| 4 | 삭제 |

| 5 | 청구항 1에 있어서, 상기 Zn1-xAlxO층은 0.5 × 1020 cm-3 내지 1.5 × 1020 cm-3 의 전하농도를 갖는 박막트랜지스터. |

| 6 | 청구항 1에 있어서, 상기 소오스/드레인 전극들과 상기 저저항층 사이에 배치되고, 상기 저저항층으로부터 산소를 흡수하는 산소 소기막(oxygen scavanging layer)을 더 포함하는 박막트랜지스터. |

| 7 | 게이트 전극; 상기 게이트 전극에 중첩하는 산화물 반도체 채널층; 상기 게이트 전극과 상기 산화물 반도체 채널층 사이에 배치된 게이트 절연막; 및 상기 산화물 반도체 채널층의 양측 단부들에 각각 전기적으로 접속하는 소오스 및 드레인 전극들을 포함하는 박막트랜지스터를 제조하되,상기 산화물 반도체 채널층과 상기 소오스/드레인 전극들 사이에 배치된 저저항층을 형성하고, 상기 저저항층은 산화물 반도체 채널층 대비 전하농도가 높은 산화물 반도체층이고,상기 저저항층은 상기 산화물 반도체 채널층을 따라 연장되어 상기 소오스/드레인 전극들 사이의 영역에서 상기 게이트 전극과 중첩하도록 배치된 Zn1-xAlxO층(x는 0초과 0.62 이하)이고, 1.7 내지 2.2 nm의 두께를 갖는 박막트랜지스터 제조방법. |

| 8 | 삭제 |

| 9 | 삭제 |

| 10 | 청구항 7에 있어서, 상기 Zn1-xAlxO층은 Al2O3를 형성하는 ALD 단위 사이클과 ZnO를 형성하는 ALD 단위 사이클을 포함하는 원자층 증착법(ALD)을 사용하여 형성하되,상기 Al2O3를 형성하는 ALD 단위 사이클의 개수와 상기 ZnO를 형성하는 ALD 단위 사이클의 개수의 비를 약 1:2 내지 1: 15로 진행하는 박막트랜지스터 제조방법. |

| 12 | 삭제 |