| 번호 | 청구항 |

|---|---|

| 1 | 게이트 전극;상기 게이트 전극의 상부 또는 하부를 가로지르는 다결정질 금속 산화물 채널층;상기 게이트 전극과 상기 다결정질 금속 산화물 채널층 사이에 배치된 절연막인 알루미늄 산화막; 및상기 다결정질 금속 산화물 채널층의 양측 단부들에 각각 전기적으로 접속하는 소오스 및 드레인 전극들을 포함하고,상기 다결정질 금속 산화물 채널층은 상기 알루미늄 산화막에 접하는 계면의 적어도 일부분에서, 비정질 매트릭스 내에 서로 이격하는 복수의 결정립들을 구비하는 것인 박막트랜지스터. |

| 2 | 제1항에 있어서,상기 알루미늄 산화막은 터널 절연막이고,상기 게이트 전극과 상기 터널 절연막 사이에 차례로 배치된 블로킹 절연막과 전하 포획층을 더 포함하는 박막트랜지스터. |

| 3 | 제1항에 있어서,상기 다결정질 금속 산화물 채널층이 상기 게이트 전극을 바라보는 면의 반대 면 상에 상기 다결정질 금속 산화물 채널층에 접하여 배치된 산화 또는 산질화된 전이금속층을 더 포함하고,상기 산화 또는 산질화된 전이금속층은 상기 게이트 전극의 적어도 중앙부와 중첩되도록 배치되는 박막트랜지스터. |

| 4 | 제1항에 있어서,상기 다결정질 금속 산화물 채널층은 In-Ga 산화물층, In-Zn 산화물층, 또는 In-Ga-Zn 산화물층인 박막트랜지스터. |

| 5 | 제4항에 있어서,상기 다결정질 금속 산화물 채널층은 C-축 결정화된 결정립들을 구비하는 박막트랜지스터. |

| 6 | 제1항에 있어서,상기 다결정질 금속 산화물 채널층의 결정화도는, 상기 다결정질 금속 산화물 채널층이 상기 게이트 전극을 바라보는 면의 반대 면에서 상기 알루미늄 산화막 방향으로 감소하는 박막트랜지스터. |

| 7 | 제1항에 있어서,상기 다결정질 금속 산화물 채널층이 상기 게이트 전극을 바라보는 면의 반대 면 상에 상기 다결정질 금속 산화물 채널층에 접하여 배치된 산화 또는 산질화된 전이금속층을 더 포함하고,상기 산화 또는 산질화된 전이금속층에 함유된 전이금속은 상기 다결정질 금속 산화물 채널층 내에 함유된 금속들 대비 산화 경향(oxidation tendency)이 큰 전이금속인 박막트랜지스터. |

| 8 | 제7항에 있어서,상기 산화 또는 산질화된 전이금속층은 Ta 산화막, Ti 산화막, Mo 산화막, Ta 산질화막(Ta oxynitride layer), Ti 산질화막, 또는 Mo 산질화막인 박막트랜지스터. |

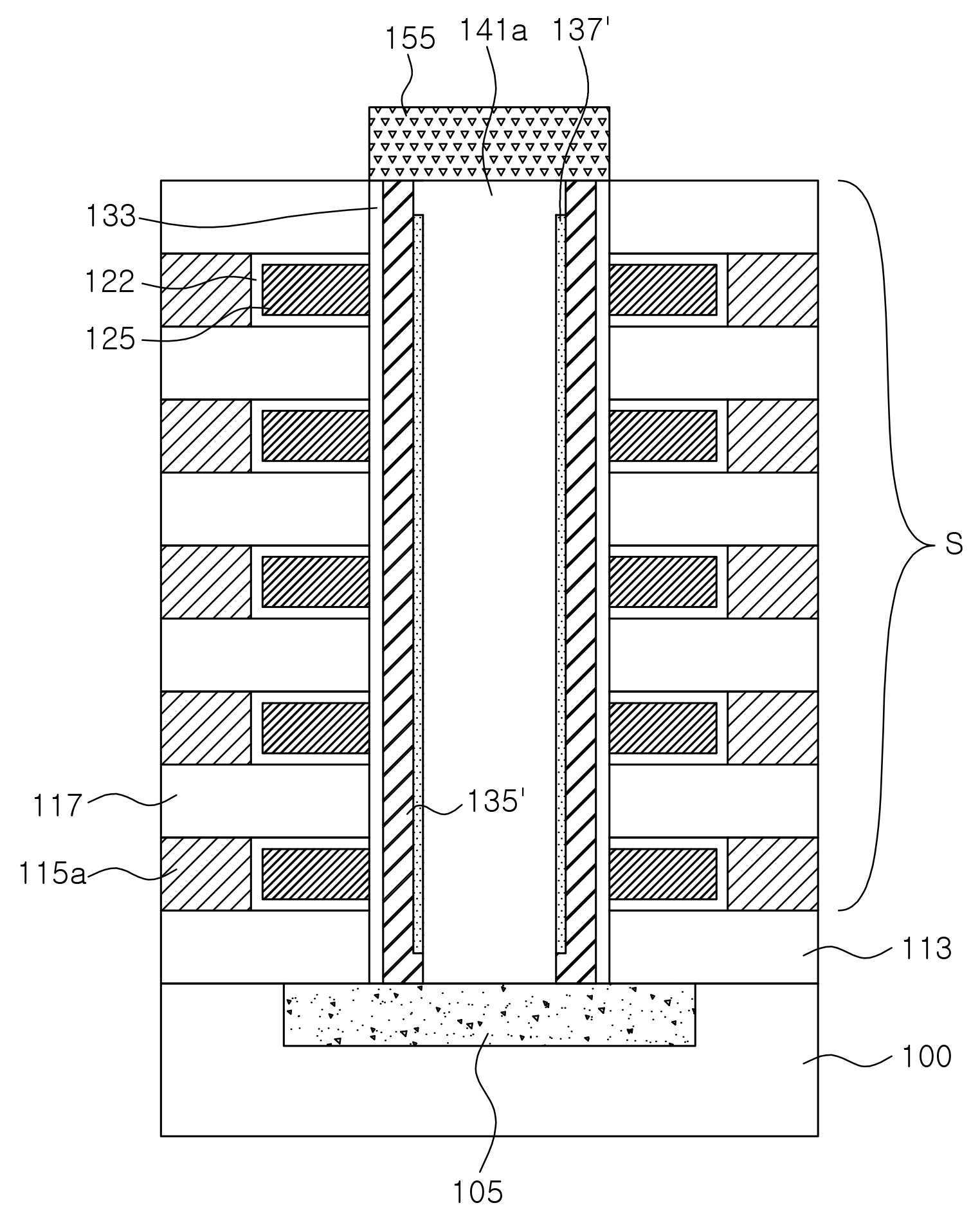

| 9 | 기판:상기 기판 상부 방향으로 연장되는 절연 기둥;상기 절연 기둥의 측부에 배치되고 교호적으로 적층된 층간 절연막들과 제어 게이트 패턴들;상기 절연 기둥과 상기 제어 게이트 패턴들 사이에서 상기 절연 기둥 상에 배치되고, 상기 절연 기둥을 따라 연장하는 다결정질 금속 산화물 채널층; 및상기 다결정질 금속 산화물 채널층과 상기 각 제어 게이트 패턴 사이에 차례로 배치된 알루미늄 산화막인 터널 절연막, 전하 포획층, 및 블로킹 절연막을 구비하고,상기 다결정질 금속 산화물 채널층은 상기 터널 절연막에 접하는 계면의 적어도 일부분에서, 비정질 매트릭스 내에 서로 이격하는 복수의 결정립들을 구비하는 것인 수직형 비휘발성 메모리 소자. |

| 10 | 제9항에 있어서,상기 알루미늄 산화막은 Al2O3층인 수직형 비휘발성 메모리 소자. |

| 11 | 제9항에 있어서,상기 다결정질 금속 산화물 채널층은 In-Ga 산화물층, In-Zn 산화물층, 또는 In-Ga-Zn 산화물층인 수직형 비휘발성 메모리 소자. |

| 12 | 제11항에 있어서,상기 다결정질 금속 산화물 채널층은 In-Ga-Zn 산화물층이고,상기 In-Ga-Zn 산화물층 내에서 In, Ga, 및 Zn의 합계 원자수 대비 In은 20 내지 80 at%를 갖는 수직형 비휘발성 메모리 소자. |

| 13 | 제11항에 있어서,상기 다결정질 금속 산화물 채널층은 C-축 결정화된 결정립들을 구비하는 수직형 비휘발성 메모리 소자. |

| 14 | 제11항에 있어서,상기 다결정질 금속 산화물 채널층은 XRD 스펙트럼 상에서 (009) 회절 피크를 나타내는 수직형 비휘발성 메모리 소자. |

| 15 | 제9항에 있어서,상기 다결정질 금속 산화물 채널층의 결정화도는 상기 절연기둥을 바라보는 표면으로부터 상기 터널 절연막 방향으로 감소하는 수직형 비휘발성 메모리 소자. |

| 16 | 제9항에 있어서,상기 절연 기둥과 상기 다결정질 금속 산화물 채널층 사이에서 상기 절연 기둥 상에 배치되고, 상기 절연 기둥을 따라 연장하는 산화 또는 산질화된 전이금속층을 더 포함하는 수직형 비휘발성 메모리 소자. |

| 17 | 제16항에 있어서,상기 산화 또는 산질화된 전이금속층에 함유된 전이금속은 상기 다결정질 금속 산화물 채널층 내에 함유된 금속들 대비 산화 경향(oxidation tendency)이 큰 전이금속인 수직형 비휘발성 메모리 소자. |

| 18 | 제17항에 있어서,상기 산화 또는 산질화된 전이금속층은 Ta 산화막, Ta 산질화막(Ta oxynitride layer), Ti 산화막, Ti 산질화막, Mo 산화막, 또는 Mo 산질화막인 수직형 비휘발성 메모리 소자. |

| 19 | 기판 상에 복수의 층간 절연막들과 복수의 제어 게이트막들을 교호적으로 적층하는 단계;상기 교호적으로 적층된 층간 절연막들과 제어 게이트막들을 관통하는 개구부를 형성하는 단계;상기 개구부의 측벽 상에 블로킹 절연막, 전하 포획층, 및 알루미늄 산화막인 터널 절연막을 차례로 형성하는 단계;상기 터널 절연막이 형성된 개구부의 측벽 상에 금속 산화물 채널층과 전이금속층을 차례로 형성하는 단계;상기 금속 산화물 채널층 상에 상기 전이금속층이 형성된 기판을 산소 분위기 또는 질소 분위기에서 열처리하여 상기 금속 산화물 채널층을 결정화하여 다결정질 금속 산화물 채널층을 형성하는 단계; 및상기 다결정질 금속 산화물 채널층이 형성된 개구부 내에 절연 기둥을 형성하는 단계를 포함하는 수직형 비휘발성 메모리 소자 제조방법. |

| 20 | 제19항에 있어서,상기 알루미늄 산화막은 원자층 증착법을 사용하여 형성한 Al2O3층인 수직형 비휘발성 메모리 소자 제조방법. |

| 21 | 제19항에 있어서,상기 금속 산화물 채널층과 전이금속층은 원자층 증착법을 사용하여 형성하는 수직형 비휘발성 메모리 소자 제조방법. |

| 22 | 제19항에 있어서,상기 금속 산화물 채널층 상에 상기 전이금속층이 형성된 기판을 산소 분위기에서 열처리하여 상기 다결정질 금속 산화물 채널층을 형성함과 동시에 상기 전이금속층을 산화시키거나,상기 금속 산화물 채널층 상에 상기 전이금속층이 형성된 기판을 질소 분위기에서 열처리하여 상기 다결정질 금속 산화물 채널층을 형성함과 동시에 상기 전이금속층을 산질화시키는 수직형 비휘발성 메모리 소자 제조방법. |

| 23 | 제19항에 있어서,상기 전이금속층에 함유된 전이금속은 상기 금속 산화물 채널층 내에 함유된 금속들 대비 산화 경향(oxidation tendency)이 큰 전이금속인 수직형 비휘발성 메모리 소자 제조방법. |

| 24 | 제19항에 있어서,상기 열처리는 200 내지 400℃의 온도범위에서 수행되는 수직형 비휘발성 메모리 소자 제조방법. |