| 번호 | 청구항 |

|---|---|

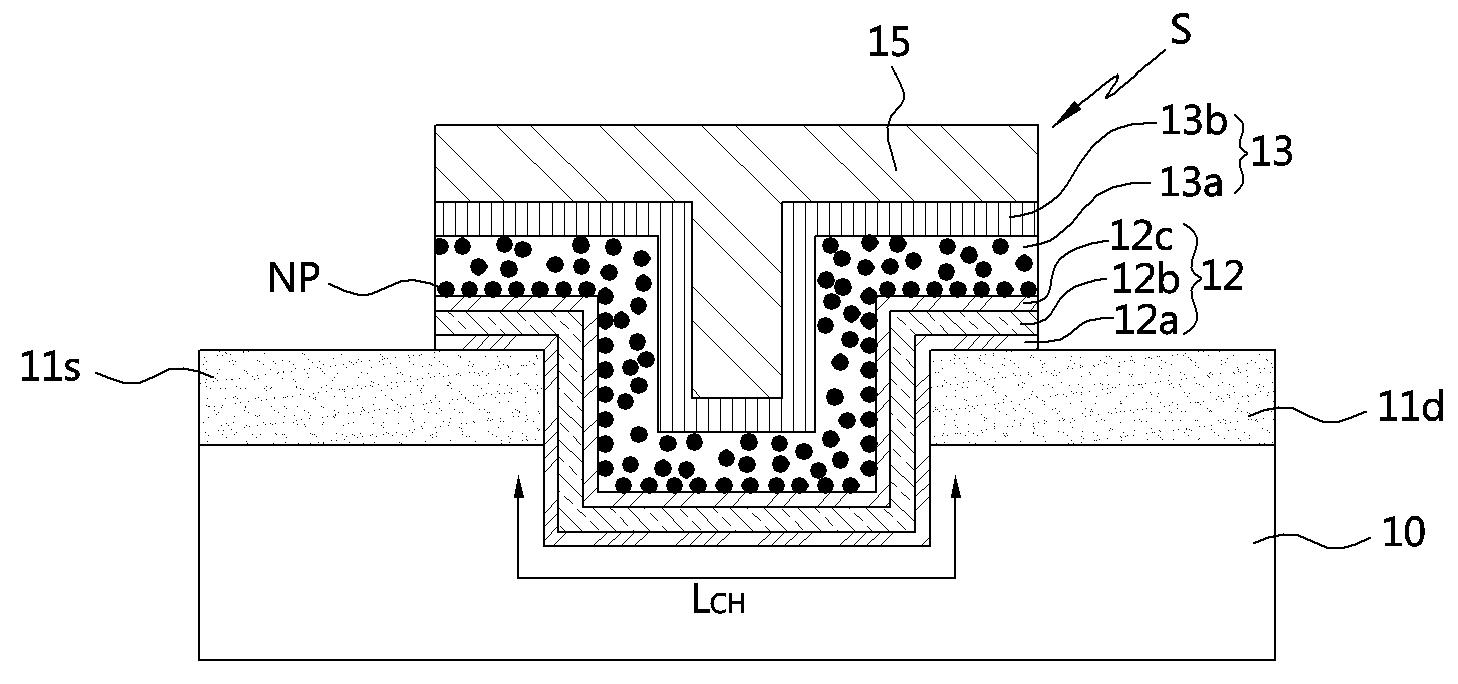

| 1 | 기판 상에 배치된 하부 실리콘 산화막, 실리콘 질화막 및 상부 실리콘 산화막을 구비하는 터널링 절연막; 상기 터널링 절연막 상에 배치된 컨트롤 절연막; 상기 컨트롤 절연막의 하부 영역 내에 다층으로 분산된 실리콘 카바이드 나노 입자들; 및 상기 컨트롤 절연막 상에 배치된 게이트 전극을 구비하는 비휘발성 메모리 소자. |

| 2 | 제1항에 있어서, 상기 하부 실리콘 산화막은 0.5nm 내지 2nm의 두께를 갖고, 상기 실리콘 질화막은 2nm 내지 7.8nm의 두께를 가지며, 상기 상부 실리콘 산화막은 0.5nm 내지 2nm의 두께를 갖는 비휘발성 메모리 소자. |

| 3 | 제2항에 있어서, 상기 하부 실리콘 산화막은 0.5nm 내지 1.5nm의 두께를 갖고, 상기 실리콘 질화막은 3.9nm 내지 7.8nm의 두께를 가지며, 상기 상부 실리콘 산화막은 0.5nm 내지 1.5nm의 두께를 갖는 비휘발성 메모리 소자. |

| 4 | 제1항에 있어서, 상기 컨트롤 절연막의 하부 영역은 하부 컨트롤 절연막이고, 상부 영역은 상부 컨트롤 절연막이고, 상기 실리콘 카바이드 나노 입자들은 상기 하부 컨트롤 절연막 내에 위치하는 비휘발성 메모리 소자. |

| 5 | 삭제 |

| 6 | 기판 상에 하부 실리콘 산화막, 실리콘 질화막 및 상부 실리콘 산화막을 구비하는 터널링 절연막을 형성하는 단계; 상기 터널링 절연막 상에 실리콘 카바이드막을 형성하는 단계; 상기 실리콘 카바이드막 상에 하부 컨트롤 절연막을 형성하는 단계; 상기 하부 컨트롤 절연막이 형성된 기판을 열처리하여 상기 하부 컨트롤 절연막 내에 다층으로 분산된 실리콘 카바이드 나노 입자들을 형성하는 단계; 및 상기 컨트롤 절연막 상에 게이트 전극막을 형성하는 단계를 포함하는 비휘발성 메모리 소자 제조방법. |

| 7 | 제6항에 있어서, 상기 하부 실리콘 산화막은 0.5nm 내지 2nm의 두께로 형성하고, 상기 실리콘 질화막은 2nm 내지 7.8nm의 두께로 형성하며, 상기 상부 실리콘 산화막은 0.5nm 내지 2nm의 두께로 형성하는 비휘발성 메모리 소자 제조방법. |

| 8 | 제7항에 있어서, 상기 하부 실리콘 산화막은 0.5nm 내지 1.5nm의 두께로 형성하고, 상기 실리콘 질화막은 3.9nm 내지 7.8nm의 두께로 형성하며, 상기 상부 실리콘 산화막은 0.5nm 내지 1.5nm의 두께로 형성하는 비휘발성 메모리 소자 제조방법. |

| 9 | 제6항에 있어서, 상기 게이트 전극막을 형성하기 전에 상기 실리콘 카바이드 나노 입자들이 형성된 하부 컨트롤 절연막 상에 상부 컨트롤 절연막을 형성하는 단계를 더 포함하는 비휘발성 메모리 소자 제조방법. |

| 10 | 삭제 |