| 번호 | 청구항 |

|---|---|

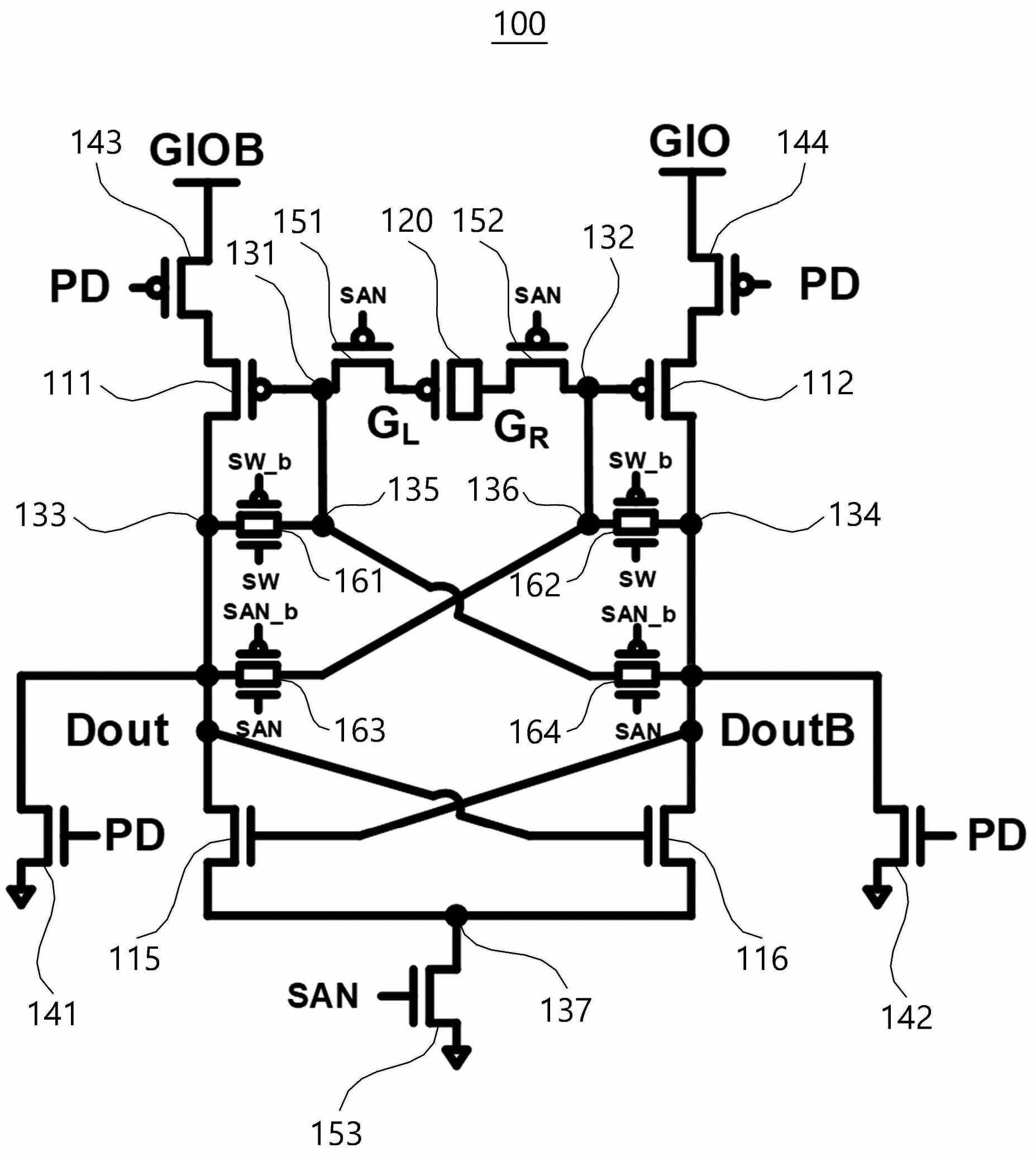

| 1 | 감지 증폭 회로(Sense Amplifier)에 있어서,소스(source)가 제1 글로벌 입출력 라인에 연결되는 제1-1 트랜지스터;소스가 제2 글로벌 입출력 라인에 연결되는 제1-2 트랜지스터; 및상기 제1-1 트랜지스터의 게이트(gate)와 상기 제1-2 트랜지스터의 게이트 사이에 연결되는 모스캡(MOS Capacitor)을 포함하는 입출력 감지 증폭 회로. |

| 2 | 제1항에 있어서,상기 제1-1 트랜지스터의 게이트와 연결되는 제1-1 노드를 통하여 상기 모스캡과 상기 제1-1 트랜지스터를 연결하는 제2-1 트랜지스터; 및상기 제1-2 트랜지스터의 게이트와 연결되는 제1-2 노드를 통하여 상기 모스캡과 상기 제1-2 트랜지스터를 연결하는 제2-2 트랜지스터를 더 포함하는 입출력 감지 증폭 회로. |

| 3 | 제2항에 있어서,상기 제1-1 트랜지스터의 드레인과 연결되는 제2-1 노드와 상기 제1-1 노드를 연결하거나 차단하는 제1-1 스위치; 및상기 제1-2 트랜지스터의 드레인과 연결되는 제2-2 노드와 상기 제1-2 노드를 연결하거나 차단하는 제1-2 스위치를 더 포함하는 입출력 감지 증폭 회로. |

| 4 | 제3항에 있어서,상기 제1-2 노드와 상기 제1-2 스위치 사이에 위치한 제3-2 노드와 상기 제2-1 노드를 연결하거나 차단하는 제2-1 스위치; 및상기 제1-1 노드와 상기 제1-1 스위치 사이에 위치한 제3-1 노드와 상기 제2-2 노드를 연결하거나 차단하는 제2-2 스위치를 더 포함하는 입출력 감지 증폭 회로. |

| 5 | 제4항에 있어서,게이트가 상기 제2-2 노드와 연결되고, 소스가 상기 제2-1 노드와 연결되는 제3-1 트랜지스터; 및게이트가 상기 제2-1 노드와 연결되고, 소스가 상기 제2-2 노드와 연결되는 제3-2 트랜지스터를 더 포함하는 입출력 감지 증폭 회로. |

| 6 | 제5항에 있어서,상기 제3-1 트랜지스터의 드레인과 상기 제3-2 트랜지스터의 드레인은 제4 노드를 통하여 연결되고,상기 제4 노드는 제5 트랜지스터의 소스와 연결되고,상기 제5 트랜지스터는 드레인이 그라운드(GND)와 연결되는 입출력 감지 증폭 회로. |

| 7 | 제6항에 있어서,소스가 상기 제2-1 노드와 연결되고, 드레인이 그라운드와 연결되는 제4-1 트랜지스터; 및소스가 상기 제2-2 노드와 연결되고, 드레인이 그라운드와 연결되는 제4-2 트랜지스터를 더 포함하는 입출력 감지 증폭 회로. |

| 8 | 제7항에 있어서,상기 제1-1 트랜지스터는, 상기 제1-1 트랜지스터의 소스와 연결되는 제5-1 트랜지스터를 통하여 상기 제1 글로벌 입출력 라인과 연결되고,상기 제1-2 트랜지스터는, 상기 제1-2 트랜지스터의 소스와 연결되는 제5-2 트랜지스터를 통하여 상기 제2 글로벌 입출력 라인과 연결되는입출력 감지 증폭 회로. |

| 9 | 제8항에 있어서,상기 제4-1 트랜지스터는, 상기 제5-1 트랜지스터와 서로 다른 채널 유형을 가지는 트랜지스터이고,상기 제4-2 트랜지스터는, 상기 제5-2 트랜지스터와 서로 다른 채널 유형을 가지는 트랜지스터인입출력 감지 증폭 회로. |

| 10 | 제9항에 있어서,상기 제4-1 트랜지스터의 게이트, 상기 제4-2 트랜지스터의 게이트, 상기 제5-1 트랜지스터의 게이트 및 상기 제5-2 트랜지스터의 게이트는 동일한 신호를 입력받는입출력 감지 증폭 회로. |

| 11 | 메모리 셀 데이터를 증폭하는 비트라인 감지 증폭 회로;상기 비트라인 감지 증폭부가 증폭한 데이터를 로컬 입출력 라인을 통하여 제공받고, 상기 로컬 입출력 라인의 데이터를 감지하여 글로벌 입출력 라인으로 데이터를 제공하는 로컬 감지 증폭 회로; 및상기 로컬 감지 증폭 회로로부터 글로벌 입출력 라인을 통하여 데이터를 제공받고, 모스캡을 이용하여 동작하며, 상기 글로벌 입출력 라인의 데이터를 감지하여 외부로 제공하는 입출력 감지 증폭 회로를 포함하는, 반도체 메모리 장치. |

| 12 | 제11항에 있어서,상기 반도체 메모리 장치는,소스(source)가 제1 글로벌 입출력 라인에 연결되는 제1-1 트랜지스터;소스가 제2 글로벌 입출력 라인에 연결되는 제1-2 트랜지스터; 및상기 제1-1 트랜지스터의 게이트(gate)와 상기 제1-2 트랜지스터의 게이트사이에 연결되는 모스캡(MOS Capacitor)을 포함하는 반도체 메모리 장치. |

| 13 | 제12항에 있어서,상기 제1-1 트랜지스터의 드레인과 연결되는 제2-1 노드와 상기 제1-1 노드를 연결하거나 차단하는 제1-1 스위치; 및상기 제1-2 트랜지스터의 드레인과 연결되는 제2-2 노드와 상기 제1-2 노드를 연결하거나 차단하는 제1-2 스위치를 더 포함하는 반도체 메모리 장치. |

| 14 | 제 8 항에 있어서,상기 입출력 감지 증폭 회로를 제어하는 컨트롤러를 더 포함하고,상기 컨트롤러는상기 제5-1 트랜지스터 및 상기 제5-2 트랜지스터를 오프(OFF)시키고,상기 제1-1 스위치 및 상기 제1-2 스위치를 온(ON)시키고,상기 제4-1 트랜지스터 및 상기 제4-2 트랜지스터를 온(ON)시키고,상기 제2-1 트랜지스터 및 상기 제2-2 트랜지스터(152)는 온(ON)시키는입출력 감지 증폭 회로. |

| 15 | 제 8 항에 있어서,상기 입출력 감지 증폭 회로를 제어하는 컨트롤러를 더 포함하고,상기 컨트롤러는상기 제1-1 스위치 및 상기 제1-2 스위치를 온(ON)시키고,상기 제2-1 트랜지스터 및 상기 제2-2 트랜지스터(152)는 온(ON)시키고,상기 제5-1 트랜지스터 및 상기 제5-2 트랜지스터를 온(ON) 시키고,상기 제4-1 트랜지스터 및 상기 제4-2 트랜지스터를 오프(OFF) 시키는입출력 감지 증폭 회로. |

| 16 | 제 8 항에 있어서,상기 입출력 감지 증폭 회로를 제어하는 컨트롤러를 포함하고,상기 컨트롤러는상기 제2-1 트랜지스터 및 상기 제2-2 트랜지스터(152)는 온(ON)시키고,상기 제1-1 스위치 및 상기 제1-2 스위치를 오프(OFF)시키고,상기 제5-1 트랜지스터 및 상기 제5-2 트랜지스터를 오프(OFF)시키고,상기 제4-1 트랜지스터 및 상기 제4-2 트랜지스터를 온(ON)시키는입출력 감지 증폭 회로. |

| 17 | 제 8 항에 있어서,상기 입출력 감지 증폭 회로를 제어하는 컨트롤러를 포함하고,상기 컨트롤러는상기 제2-1 트랜지스터 및 상기 제2-2 트랜지스터(152)는 온(ON)시키고,상기 제1-1 스위치 및 상기 제1-2 스위치를 오프(OFF)시키고,상기 제5-1 트랜지스터 및 상기 제5-2 트랜지스터를 온(ON)시키고,상기 제4-1 트랜지스터 및 상기 제4-2 트랜지스터를 오프(OFF)시키는입출력 감지 증폭 회로. |

| 18 | 제 8 항에 있어서,상기 입출력 감지 증폭 회로를 제어하는 컨트롤러를 포함하고,상기 컨트롤러는상기 제2-1 트랜지스터 및 상기 제2-2 트랜지스터(152)는 오프(OFF)시키고,상기 제1-1 스위치 및 상기 제1-2 스위치를 오프(OFF)시키고,상기 제5-1 트랜지스터 및 상기 제5-2 트랜지스터를 온(ON)시키고,상기 제4-1 트랜지스터 및 상기 제4-2 트랜지스터를 오프(OFF)시키고,상기 제2-1 스위치 및 상기 제2-2 스위치를 온(ON)시키고,상기 제3-1 트랜지스터 및 상기 제3-2 트랜지스터를 온(ON)시키고,상기 제5 트랜지스터를 온(ON)시키는입출력 감지 증폭 회로. |