| 번호 | 청구항 |

|---|---|

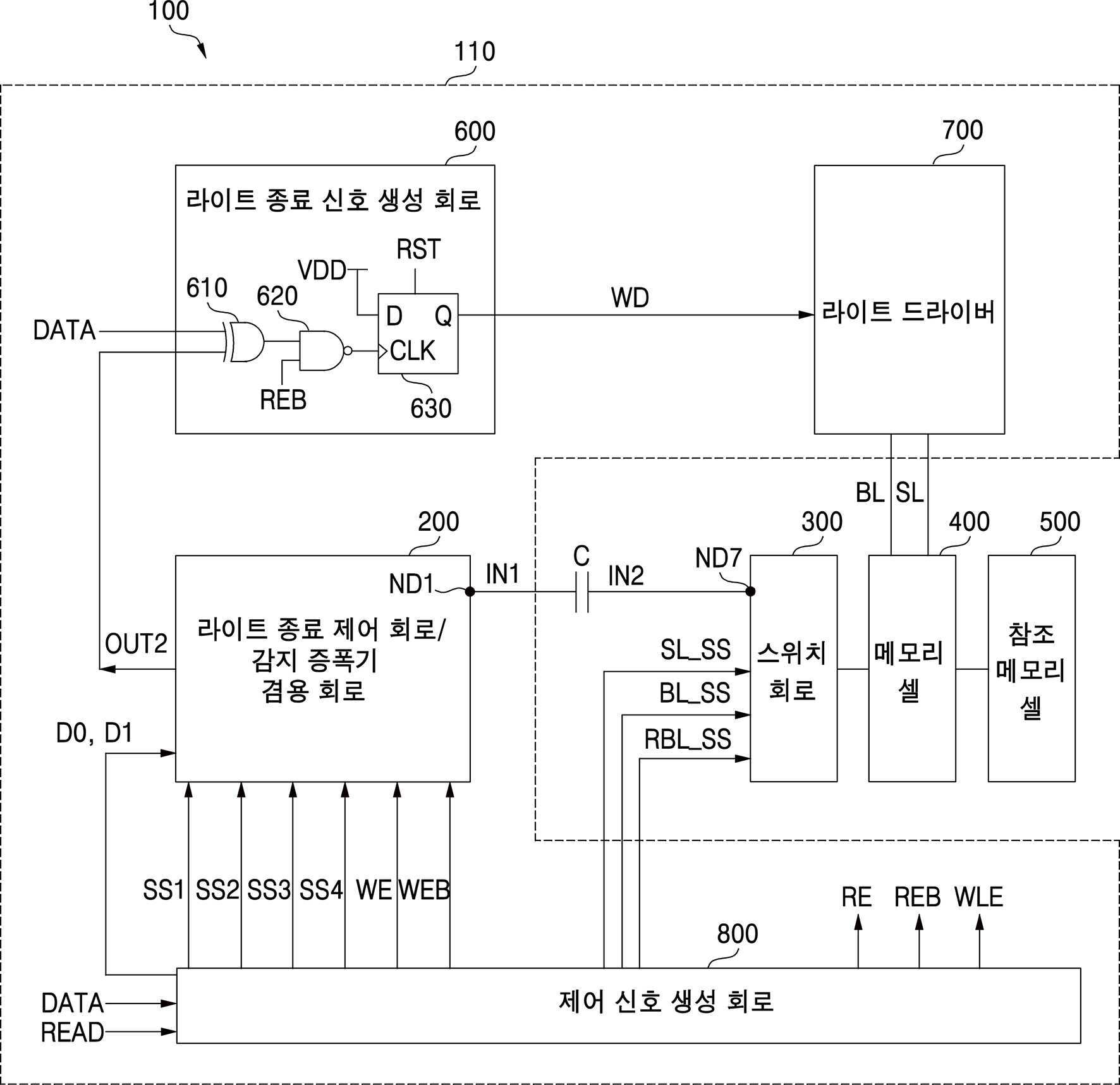

| 10 | 메모리 셀;참조 메모리 셀; 및상기 메모리 셀에 데이터를 라이트하는 라이트 드라이버를 포함하고, 상기 데이터가 상기 메모리 셀에 라이트 완료됨을 감지하여 상기 라이트 드라이버의 작동을 종료시킬뿐만 아니라, 상기 참조 메모리 셀의 출력 신호와 상기 메모리 셀의 출력 신호를 하나의 제1입력 노드를 통해 순차적으로 수신하여 상기 메모리 셀에 저장된 데이터를 감지하고 증폭하는 듀얼 모드 인버터 기반 라이트 종료 회로를 포함하는 메모리 장치. |

| 8 | 듀얼 모드 인버터 기반 라이트 종료 회로의 작동 방법에 있어서,상기 듀얼 모드 인버터 기반 라이트 종료 회로가 작동 모드 제어 신호에 응답하여 상기 듀얼 모드 인버터 기반 라이트 종료 회로를 라이트 종료 제어 회로와 감지 증폭기 중 어느 하나로 사용할지를 결정하는 단계;상기 결정의 결과에 따라 상기 듀얼 모드 인버터 기반 라이트 종료 회로를 상기 라이트 종료 제어 회로로 사용하기 위해, 상기 듀얼 모드 인버터 기반 라이트 종료 회로에 포함된 스위치들을 제1스위치 배열로 배열시키는 단계; 및상기 결정의 결과에 따라 상기 듀얼 모드 인버터 기반 라이트 종료 회로를 상기 감지 증폭기로 사용하기 위해, 상기 스위치들을 제2스위치 배열로 배열시키는 단계를 포함하는,듀얼 모드 인버터 기반 라이트 종료 회로의 작동 방법. |

| 1 | 듀얼 모드 인버터 기반 라이트 종료 회로에 있어서,제1입력 신호를 수신하는 제1입력 노드, 제1출력 신호를 출력하는 제1출력 노드, 및 상기 제1입력 노드와 상기 제1출력 노드 사이에 접속된 제1스위치를 포함하는 제1인버터;제2입력 노드와 제2출력 노드를 포함하는 제2인버터;상기 제1출력 노드와 상기 제2입력 노드 사이에 접속된 제2스위치;제1제어 신호에 응답하여 상기 제2입력 노드를 제1 전압으로 풀-업하기 위한 제2풀-업 회로;제2제어 신호에 응답하여 상기 제2입력 노드를 제2 전압으로 풀-다운하기 위한 제2풀-다운 회로; 및상기 제2출력 노드의 제2출력 신호를 유지하기 위한 전압 유지 회로를 포함하고,상기 듀얼 모드 인버터 기반 라이트 종료 회로는 라이트 종료 제어 회로와 감지 증폭기 겸용으로 사용되는 듀얼 모드 인버터 기반 라이트 종료 회로. |

| 2 | 제1항에 있어서,상기 제2출력 신호와 데이터를 배타 논리합 연산하는 배타 논리합 회로;상기 배타 논리합 회로의 출력 신호와 반전 리드 인에이블 신호를 NAND 연산하는 NAND 회로;상기 NAND 회로의 출력 신호를 수신하는 클럭 단자, 상기 제1 전압을 수신하는 입력 단자, 및 라이트 종료 신호를 출력하는 출력 단자를 포함하는 D 플립 플롭; 및상기 라이트 종료 신호에 응답하여 스핀-전달 토크 자기 저항성 메모리에 대한 라이트 작동과 라이트 종료 작동 중 어느 하나를 수행하는 라이트 드라이버를 더 포함하는 듀얼 모드 인버터 기반 라이트 종료 회로. |

| 3 | 제1항에 있어서, 상기 제1인버터는,상기 제1 전압을 전송하는 전압 전송선과 상기 제1출력 노드 사이에 접속된 스택된 제1그룹의 PMOS 트랜지스터들; 및상기 제1출력 노드와 상기 제2 전압을 전송하는 접지 사이에 접속된 스택된 제1그룹 NMOS 트랜지스터들을 더 포함하는 듀얼 모드 인버터 기반 라이트 종료 회로. |

| 4 | 제3항에 있어서, 상기 제2인버터는,상기 전압 전송선과 상기 제2출력 노드 사이에 직렬로 접속된 제2그룹의 PMOS 트랜지스터들;상기 제2출력 노드와 상기 접지 사이에 직렬로 접속된 제2그룹의 NMOS 트랜지스터들; 및상기 제1출력 노드와 상기 제2출력 노드 사이에 접속된 제3 스위치를 포함하고,상기 제2그룹의 PMOS 트랜지스터들 각각의 게이트와 상기 제2그룹의 NMOS 트랜지스터들 각각의 게이트는 상기 제2입력 노드에 접속된 듀얼 모드 인버터 기반 라이트 종료 회로. |

| 5 | 제4항에 있어서, 상기 전압 유지 회로는,상기 제2그룹의 PMOS 트랜지스터들의 제1공통 노드와 상기 접지 사이에 직렬로 접속된 PMOS 트랜지스터와 제4 스위치; 및상기 제2그룹의 NMOS 트랜지스터들의 제2공통 노드와 상기 전압 전송선 사이에 직렬로 접속된 NMOS 트랜지스터와 제5 스위치를 포함하고,상기 PMOS 트랜지스터와 상기 NMOS 트랜지스터 각각의 게이트는 상기 제2출력 노드에 접속된 듀얼 모드 인버터 기반 라이트 종료 회로. |

| 6 | 제5항에 있어서,상기 듀얼 모드 인버터 기반 라이트 종료 회로가 상기 라이트 종료 제어 회로로 사용될 때, 상기 제3 스위치는 항상 오프 상태이고 상기 제4 스위치와 상기 제5 스위치는 항상 온 상태이고,상기 듀얼 모드 인버터 기반 라이트 종료 회로가 상기 감지 증폭기로 사용될 때, 상기 제4 스위치와 상기 제5 스위치는 항상 오프 상태인,듀얼 모드 인버터 기반 라이트 종료 회로. |

| 7 | 제6항에 있어서,상기 제2출력 신호와 데이터를 배타 논리합 연산하는 배타 논리합 회로;상기 배타 논리합 회로의 출력 신호와 반전 리드 인에이블 신호를 NAND 연산하는 NAND 회로;상기 NAND 회로의 출력 신호를 수신하는 클럭 단자, 상기 제1 전압을 수신하는 입력 단자, 및 라이트 종료 신호를 출력하는 D 플립 플롭; 및상기 라이트 종료 신호에 응답하여 스핀-전달 토크 자기 저항성 메모리에 대한 라이트 작동과 라이트 종료 작동 중 어느 하나를 수행하는 라이트 드라이버를 더 포함하는 듀얼 모드 인버터 기반 라이트 종료 회로. |

| 9 | 제8항에 있어서,상기 제1스위치 배열을 이용하여, 메모리의 출력 신호를 수신하는 상기 듀얼 모드 인버터 기반 라이트 종료 회로에 포함된 인버터의 입력 노드와 출력 노드를 접속하여 오프셋을 제거하는 단계를 더 포함하는,듀얼 모드 인버터 기반 라이트 종료 회로의 작동 방법. |

| 11 | 제10항에 있어서, 상기 듀얼 모드 인버터 기반 라이트 종료 회로는,상기 데이터와 상기 듀얼 모드 인버터 기반 라이트 종료 회로로부터 출력된 제2출력 신호를 배타 논리합 연산하는 배타 논리합 회로;상기 배타 논리합 회로의 출력 신호와 반전 리드 인에이블 신호를 NAND 연산하는 NAND 회로; 및상기 NAND 회로의 출력 신호를 수신하는 클럭 단자, 제1전압을 수신하는 입력 단자, 및 라이트 종료 신호를 출력하는 출력 단자를 포함하는 D 플립 플롭를 포함하고,상기 라이트 드라이버는,제1레벨을 갖는 상기 라이트 종료 신호에 응답하여 상기 데이터를 상기 메모리 셀에 라이트하고,제2레벨을 갖는 상기 라이트 종료 신호에 응답하여 디스에이블되는 메모리 장치. |

| 12 | 제10항에 있어서, 상기 듀얼 모드 인버터 기반 라이트 종료 회로는,상기 제1입력 노드와 제1출력 신호를 출력하는 제1출력 노드를 포함하는 제1인버터; 및상기 제1입력 노드와 상기 제1출력 노드 사이에 접속된 제1스위치를 포함하는 메모리 장치. |

| 13 | 제12항에 있어서, 상기 제1인버터는,제1 전압을 전송하는 전압 전송선과 상기 제1출력 노드 사이에 접속된 스택된 PMOS 트랜지스터들; 및상기 제1출력 노드와 제2 전압을 전송하는 접지 사이에 접속된 스택된 NMOS 트랜지스터들을 포함하고,상기 PMOS 트랜지스터들 중 어느 하나의 게이트와 상기 NMOS 트랜지스터들 중 어느 하나의 게이트는 상기 제1입력 노드에 접속된 메모리 장치. |

| 14 | 제12항에 있어서, 상기 듀얼 모드 인버터 기반 라이트 종료 회로는,제2입력 노드와 제2출력 노드를 포함하는 제2인버터;상기 제1출력 노드와 상기 제2입력 노드 사이에 접속된 제2스위치;제1제어 신호에 응답하여 상기 제2입력 노드를 제1 전압으로 풀-업하기 위한 제2풀-업 회로;제2제어 신호에 응답하여 상기 제2입력 노드를 제2 전압으로 풀-다운하기 위한 제2풀-다운 회로; 및상기 제2출력 노드의 제2출력 신호를 유지하기 위한 전압 유지 회로를 더 포함하는 메모리 장치. |

| 15 | 제14항에 있어서, 상기 제2인버터는,상기 제1 전압을 전송하는 전압 전송선과 상기 제2출력 노드 사이에 직렬로 접속된 PMOS 트랜지스터들;상기 제2출력 노드와 상기 제2 전압을 전송하는 접지 사이에 직렬로 접속된 NMOS 트랜지스터들; 및상기 제1출력 노드와 상기 제2출력 노드 사이에 접속된 제3스위치를 포함하고,상기 PMOS 트랜지스터들 각각의 게이트와 상기 NMOS 트랜지스터들 각각의 게이트는 상기 제2입력 노드에 접속된 메모리 장치. |

| 16 | 제15항에 있어서, 상기 전압 유지 회로는,상기 PMOS 트랜지스터들의 제1공통 노드와 상기 접지 사이에 직렬로 접속된 PMOS 트랜지스터; 및상기 NMOS 트랜지스터들의 제2공통 노드와 상기 전압 전송선 사이에 직렬로 접속된 NMOS 트랜지스터와 제5스위치를 포함하고,상기 PMOS 트랜지스터와 상기 NMOS 트랜지스터 각각의 게이트는 상기 제2출력 노드에 접속된 메모리 장치. |

| 17 | 데이터를 출력하는 프로세서; 및상기 데이터를 수신하는 메모리 장치를 포함하고,상기 메모리 장치는,메모리 셀;참조 메모리 셀; 및상기 메모리 셀에 데이터를 라이트하는 라이트 드라이버를 포함하고, 상기 데이터가 상기 메모리 셀에 라이트 완료됨을 감지하여 상기 라이트 드라이버의 작동을 종료시킬뿐만 아니라, 상기 참조 메모리 셀의 출력 신호와 상기 메모리 셀의 출력 신호를 하나의 제1입력 노드를 통해 순차적으로 수신하여 상기 메모리 셀에 저장된 데이터를 감지하고 증폭하는 듀얼 모드 인버터 기반 라이트 종료 회로를 포함하는 메모리 시스템. |

| 18 | 제17항에 있어서, 상기 듀얼 모드 인버터 기반 라이트 종료 회로는,상기 제1입력 노드와 제1출력 신호를 출력하는 제1출력 노드를 포함하는 제1인버터;제2입력 노드와 제2출력 노드를 포함하는 제2인버터;상기 제1출력 노드와 상기 제2입력 노드 사이에 접속된 제2스위치;제1제어 신호에 응답하여 상기 제2입력 노드를 제1 전압으로 풀-업하기 위한 제2풀-업 회로;제2제어 신호에 응답하여 상기 제2입력 노드를 제2 전압으로 풀-다운하기 위한 제2풀-다운 회로; 및상기 제2출력 노드의 제2출력 신호를 유지하기 위한 전압 유지 회로를 포함하는 메모리 시스템. |

| 19 | 제18항에 있어서, 상기 제1인버터는,상기 제1 전압을 전송하는 전압 전송선과 상기 제1출력 노드 사이에 접속된 스택된 제1그룹의 PMOS 트랜지스터들;상기 제1출력 노드와 상기 제2 전압을 전송하는 접지 사이에 접속된 스택된 제1그룹 NMOS 트랜지스터들; 및상기 제1입력 노드와 상기 제1출력 노드 사이에 접속된 제1스위치를 포함하는 메모리 시스템. |

| 20 | 제18항에 있어서, 상기 듀얼 모드 인버터 기반 라이트 종료 회로는,상기 데이터와 상기 듀얼 모드 인버터 기반 라이트 종료 회로의 출력 신호를 배타 논리합 연산하는 배타 논리합 회로;상기 배타 논리합 회로의 출력 신호와 반전 리드 인에이블 신호를 NAND 연산하는 NAND 회로; 및상기 NAND 회로의 출력 신호를 수신하는 클럭 단자, 상기 제1 전압을 수신하는 입력 단자, 및 라이트 종료 신호를 출력하는 출력 단자를 포함하는 플립 플롭을 포함하고,상기 라이트 드라이버는 상기 라이트 종료 신호의 레벨에 따라 상기 데이터를 상기 메모리 셀에 라이트하거나 디스에이블되는 메모리 시스템. |