| 번호 | 청구항 |

|---|---|

| 1 | 입력 데이터의 최상위 비트(이하 MSB)의 비트값에 따라 출력 노드를 전원 전압 또는 접지 전압 레벨로 프리차지 하는 프리차지 회로; 상기 입력 데이터의 MSB를 제외한 나머지 비트의 값에 따른 펄스 폭을 갖는 펄스 신호를 획득하고, 상기 펄스 신호와 상기 MSB에 따른 펄스 폭을 갖는 차지 신호를 생성하는 펄스 제어 회로; 및 전원 전압 또는 접지 전압 레벨로 프리차지된 상기 출력 노드의 전압 레벨을 상기 차지 신호에 따라 상승 또는 하강시켜 상기 입력 데이터에 대응하는 전압 레벨로 조절하는 2방향 차지 회로를 포함하되,상기 프리차지 회로는 전원 전압과 상기 출력 노드 사이에 연결되는 제1 프리차지 트랜지스터와 상기 출력 노드와 접지 전압 사이에 연결되는 제2 프리차지 트랜지스터, 상기 입력 데이터를 제공하는 컨트롤러로부터 반전 프리차지 신호를 인가받아 반전하여 프리차지 신호를 출력하는 제4 인버터, 상기 MSB를 인가받아 반전하여 출력하는 제5 인버터, 상기 MSB와 상기 제4 인버터의 출력을 인가받아 부정 논리곱하여 상기 제1 프리차지 트랜지스터의 게이트로 인가하는 제3 낸드 게이트, 상기 제4 인버터의 출력과 상기 제5 인버터의 출력을 인가받아 부정 논리곱하는 제4 낸드 게이트, 및 상기 제4 낸드 게이트의 출력을 반전하여 상기 제2 프리차지 트랜지스터의 게이트로 인가하는 제6 인버터를 포함하는 DAC. |

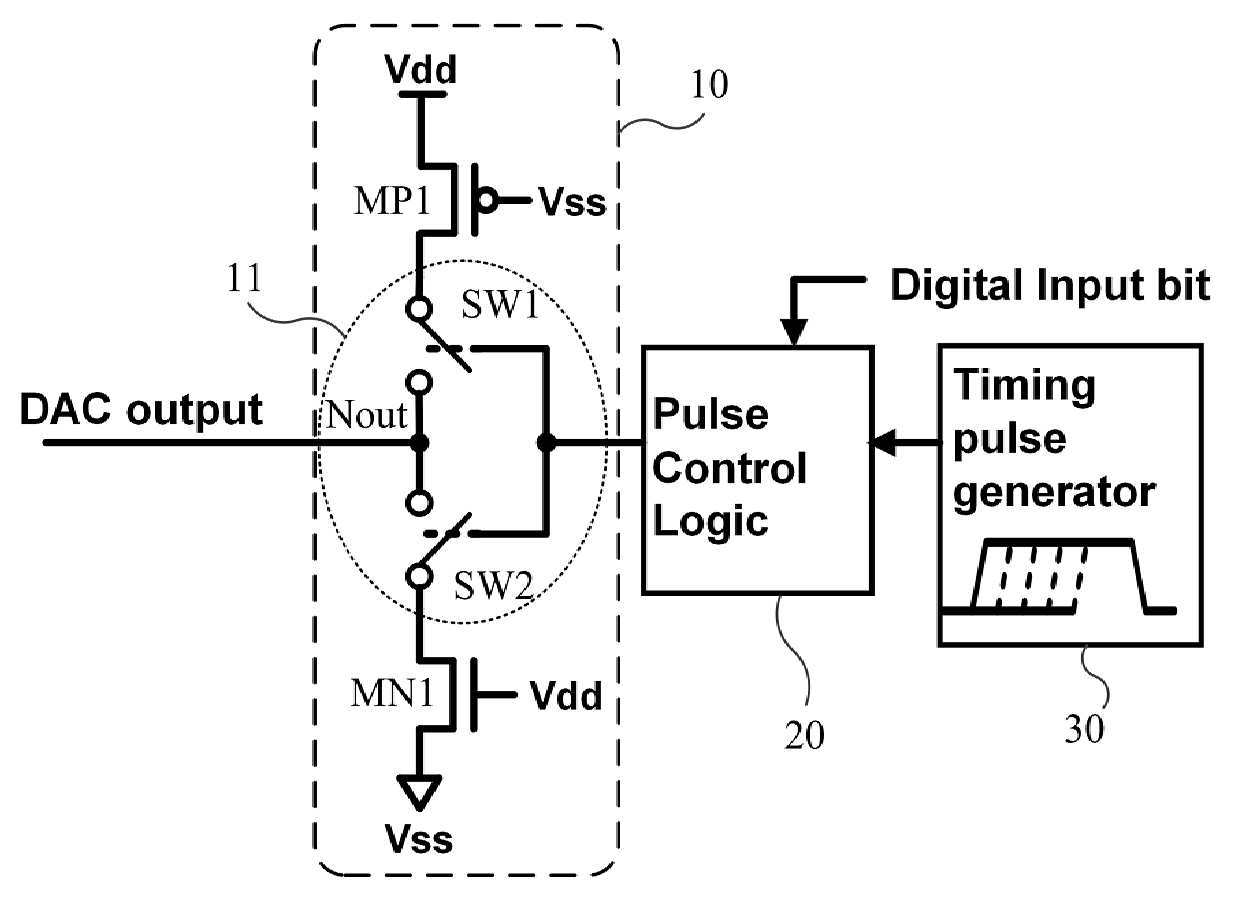

| 2 | 제1항에 있어서, 상기 2방향 차지 회로는 상기 전원 전압에 일단이 연결되는 풀업 트랜지스터와 상기 접지 전압에 일단이 연결되는 풀다운 트랜지스터, 및 상기 차지 신호에 따라 상기 풀업 트랜지스터와 상기 풀다운 트랜지스터중 하나를 상기 출력 노드와 전기적으로 연결하는 스위치 회로를 포함하는 DAC. |

| 3 | 제2항에 있어서, 상기 스위치 회로는 상기 차지 신호 중 상기 MSB의 비트값이 0이면 활성화되어 펄스 형태를 갖는 제1 차지 신호의 펄스 폭에 따른 시간 동안 상기 풀업 트랜지스터의 타단과 상기 출력 노드를 전기적으로 연결하는 제1 스위치와 상기 차지 신호 중 상기 MSB의 비트값이 1이면 활성화되어 펄스 형태를 갖는 제2 차지 신호의 펄스 폭에 따른 시간 동안 상기 풀다운 트랜지스터의 타단과 상기 출력 노드를 전기적으로 연결하는 제2 스위치를 포함하는 DAC. |

| 4 | 제3항에 있어서, 상기 제1 차지 신호는 상기 나머지 비트의 값에 비례하여 증가되는 펄스 폭을 갖고, 상기 제2 차지 신호는 상기 나머지 비트의 값에 비례하여 감소되는 펄스 폭을 갖는 DAC. |

| 5 | 제3항에 있어서, 상기 제1 스위치는 게이트로 상기 제1 차지 신호를 인가받는 PMOS 트랜지스터로 구현되고, 상기 제2 스위치는 게이트로 상기 제2 차지 신호를 인가받는 NMOS 트랜지스터로 구현되는 DAC. |

| 6 | 제1항에 있어서, 상기 펄스 제어 회로는 상기 입력 데이터에서 상기 나머지 비트의 값에 따른 펄스 폭을 갖는 상기 펄스 신호를 생성하는 펄스 생성 회로와 생성된 상기 펄스 신호를 인가받고, 상기 MSB의 비트값이 0이면 활성화되어 펄스 형태를 갖는 제1 차지 신호와 상기 MSB의 비트값이 1이면 활성화되어 펄스 형태를 갖는 제2 차지 신호를 생성하는 차지 신호 생성 회로를 포함하는 DAC. |

| 7 | 제6항에 있어서, 상기 펄스 생성 회로는 상기 나머지 비트의 값이 클수록 긴 펄스 폭을 갖는 상기 펄스 신호를 생성하는 DAC. |

| 8 | 제6항에 있어서, 상기 차지 신호 생성 회로는 상기 MSB의 비트값이 0이면, 상기 펄스 신호가 반전된 상기 제1 차지 신호를 상기 2방향 차지 회로로 출력하는 제1 차지 신호 생성 회로와 상기 MSB의 비트값이 1이면, 상기 펄스 신호와 상기 펄스 생성 회로에서 생성되는 펄스들 중 가장 긴 펄스 폭을 가지는 기준 펄스 신호 사이의 펄스 폭 차이만큼의 펄스 폭을 갖는 상기 제2 차지 신호를 상기 2방향 차지 회로로 출력하는 제2 차지 신호 생성 회로를 포함하는 DAC. |

| 9 | 제8항에 있어서, 상기 제1 차지 신호 생성 회로는 상기 MSB를 인가받아 반전하는 제1 인버터와 상기 제1 인버터의 출력과 상기 펄스 신호를 부정 논리곱하여 상기 제1 차지 신호를 생성하는 제1 낸드 게이트를 포함하는 DAC. |

| 10 | 제8항에 있어서, 상기 제2 차지 신호 생성 회로는 상기 펄스 신호를 인가받아 반전하는 제2 인버터와 상기 나머지 비트의 값이 최대값인 경우에 획득되는 가장 큰 펄스 폭을 갖는 펄스 신호인 기준 펄스 신호와 상기 제2 인버터의 출력 및 상기 MSB를 부정 논리곱하는 제2 낸드 게이트, 및 상기 제2 낸드 게이트의 출력을 반전하여 상기 제2 차지 신호를 생성하는 제3 인버터를 포함하는 DAC. |

| 11 | 제1항에 있어서, 상기 프리차지 회로는 상기 MSB의 비트값이 0이면 상기 출력 노드를 접지 전압 레벨로 프리차지하고, 상기 MSB의 비트값이 1이면 상기 출력 노드를 전원 전압 레벨로 프리차지하는 DAC. |

| 12 | 삭제 |

| 13 | 제1항에 있어서, 상기 제1 프리차지 트랜지스터는 PMOS 트랜지스터로 구현되고, 상기 제2 프리차지 트랜지스터는 NMOS 트랜지스터로 구현되는 DAC. |