| 번호 | 청구항 |

|---|---|

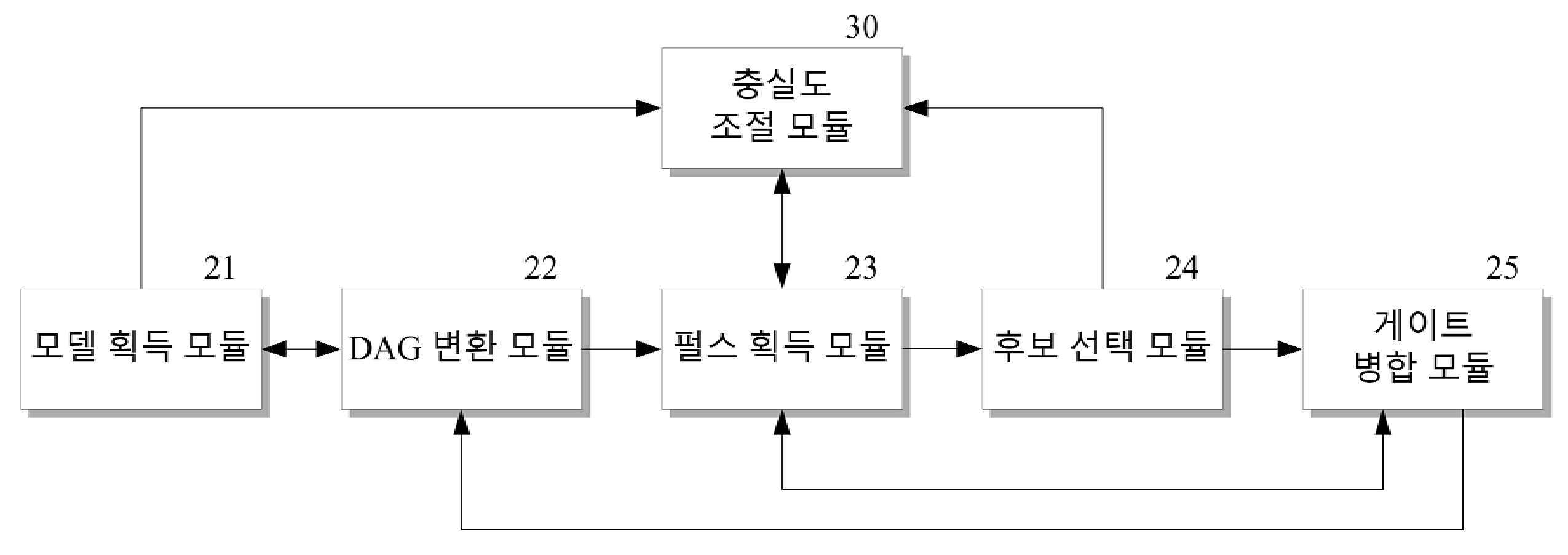

| 1 | 메모리; 및 상기 메모리에 저장된 프로그램에 따른 동작의 적어도 일부를 실행하는 프로세서를 포함하는 장치로서, 상기 프로세서는 적어도 하나의 큐빗과 다수의 양자 게이트로 구성된 양자 회로 모델에서 상기 다수의 양자 게이트 각각에 대한 양자 펄스를 획득하고, 획득된 양자 펄스의 길이를 기반으로 병합 대상 후보 양자 게이트를 선택하여 임시 병합하며, 임시 병합된 병합 양자 게이트에 대한 양자 펄스 길이가 기준 펄스 길이 미만이면, 선택된 상기 후보 양자 게이트를 상기 병합 양자 게이트로 대체하는 양자 회로 모델의 양자 게이트 병합 장치. |

| 2 | 제1항에 있어서, 상기 프로세서는 상기 양자 펄스의 길이가 상기 기준 양자 펄스 길이 미만인 양자 게이트를 병합 대상이 되는 후보 노드 집합에 포함시키고, 상기 후보 노드 집합에 포함된 양자 게이트 중에서 지정된 개수의 양자 게이트를 상기 후보 양자 게이트로 선택하는 양자 게이트 병합 장치. |

| 3 | 제1항에 있어서, 상기 프로세서는 설정된 요구 충족도와 요구 펄스 길이를 만족하도록 양자 펄스를 획득하는 양자 게이트 병합 장치. |

| 4 | 제3항에 있어서, 상기 기준 펄스 길이는 상기 요구 펄스 길이보다 짧으며, 상기 양자 회로 모델에서 상기 양자 게이트 각각에 연결되는 큐빗 수에 따라 상이한 길이로 설정되는 양자 게이트 병합 장치. |

| 5 | 제1항에 있어서, 상기 프로세서는 상기 양자 회로 모델의 양자 게이트가 노드로 표현되는 DAG(Directed Acyclic Graph)로 변환하는 양자 게이트 병합 장치. |

| 6 | 제5항에 있어서, 상기 프로세서는 변환된 상기 DAG에서 상기 노드들 사이의 연결 관계에 따라 병합 대상이 되는 상기 후보 양자 게이트를 선택하는 양자 게이트 병합 장치. |

| 7 | 제6항에 있어서, 상기 프로세서는 상기 양자 게이트의 큐빗 수가 기준 큐빗 수를 초과하면, 기준 큐빗 개수 이하가 되도록 양자 게이트를 분할하여 초기 DAG를 생성하고, 상기 후보 양자 게이트가 병합되면, 상기 DAG에서 상기 후보 양자 게이트 각각에 대한 노드를 하나의 노드로 병합하는 양자 게이트 병합 장치. |

| 8 | 제1항에 있어서, 상기 프로세서는 병합 가능한 상기 후보 양자 게이트가 모두 병합되어 상기 양자 회로 모델이 수정되면, 수정된 양자 회로 모델에 포함된 양자 게이트 각각에 대한 양자 펄스 길이와 상기 기준 펄스 길이에 따라 상기 양자 펄스에 요구되는 충실도를 조절하는 양자 게이트 병합 장치. |

| 9 | 제8항에 있어서, 상기 프로세서는 상기 수정된 양자 회로 모델에 포함된 양자 게이트 각각에 대해 설정된 요구 충실도와 요구 펄스 길이를 만족하는 양자 펄스를 획득하고, 획득된 상기 양자 펄스의 길이 중 상기 기준 펄스 길이보다 짧은 길이를 갖는 양자 펄스에 대한 양자 게이트를 선택하며, 선택된 양자 게이트에 대한 요구 충실도를 조절하여, 조절된 요구 충실도에 따른 양자 펄스를 다시 획득하는 양자 게이트 병합 장치. |

| 10 | 제9항에 있어서, 상기 프로세서는 상기 기준 펄스 길이보다 짧은 길이를 갖는 양자 펄스 각각의 길이에 따라 상기 요구 충실도를 차등 조절하는 양자 게이트 병합 장치. |

| 11 | 프로세서에 의해 수행되는 방법으로서, 적어도 하나의 큐빗과 다수의 양자 게이트로 구성된 양자 회로 모델에서 상기 다수의 양자 게이트 각각에 대한 양자 펄스를 획득하는 단계; 획득된 양자 펄스의 길이를 기반으로 병합 대상 후보 양자 게이트를 선택하여 임시 병합하는 단계; 및 임시 병합된 병합 양자 게이트에 대한 양자 펄스 길이가 기준 펄스 길이 미만이면, 선택된 상기 후보 양자 게이트를 상기 병합 양자 게이트로 대체하는 단계를 포함하는 양자 회로 모델의 양자 게이트 병합 방법. |

| 12 | 제11항에 있어서, 상기 임시 병합하는 단계는 상기 양자 펄스의 길이가 상기 기준 양자 펄스 길이 미만인 양자 게이트를 병합 대상이 되는 후보 노드 집합에 포함시키고, 상기 후보 노드 집합에 포함된 양자 게이트 중에서 지정된 개수의 양자 게이트를 상기 후보 양자 게이트로 선택하는 양자 게이트 병합 방법. |

| 13 | 제11항에 있어서, 상기 양자 펄스를 획득하는 단계는 설정된 요구 충족도와 요구 펄스 길이를 만족하도록 양자 펄스를 획득하는 양자 게이트 병합 방법. |

| 14 | 제13항에 있어서, 상기 기준 펄스 길이는 상기 요구 펄스 길이보다 짧으며, 상기 양자 회로 모델에서 상기 양자 게이트 각각에 연결되는 큐빗 수에 따라 상이한 길이로 설정되는 양자 게이트 병합 방법. |

| 15 | 제11항에 있어서, 상기 양자 펄스를 획득하는 단계는 상기 양자 회로 모델의 양자 게이트가 노드로 표현되는 DAG(Directed Acyclic Graph)로 변환하되, 상기 양자 게이트의 큐빗 수가 기준 큐빗 수를 초과하면, 기준 큐빗 개수 이하가 되도록 양자 게이트를 분할하여 초기 DAG를 생성하는 양자 게이트 병합 방법. |

| 16 | 제15항에 있어서, 상기 임시 병합하는 단계는 변환된 DAG에서 상기 노드들 사이의 연결 관계에 따라 병합 대상이 되는 상기 후보 양자 게이트를 선택하는 양자 게이트 병합 방법. |

| 17 | 제16항에 있어서, 상기 병합 양자 게이트로 대체하는 단계는 상기 후보 양자 게이트가 병합되면, 상기 DAG에서 상기 후보 양자 게이트 각각에 대한 노드를 하나의 노드로 병합하는 양자 게이트 병합 방법. |

| 18 | 제11항에 있어서, 상기 양자 게이트 병합 방법은 병합 가능한 상기 후보 양자 게이트가 모두 병합되어 상기 양자 회로 모델이 수정되면, 수정된 양자 회로 모델에 포함된 양자 게이트 각각에 대한 양자 펄스 길이와 상기 기준 펄스 길이에 따라 상기 양자 펄스에 요구되는 충실도를 조절하는 단계를 더 포함하는 양자 게이트 병합 방법. |

| 19 | 제18항에 있어서, 상기 충실도를 조절하는 단계는 상기 수정된 양자 회로 모델에 포함된 양자 게이트 각각에 대해 설정된 요구 충실도와 요구 펄스 길이를 만족하는 양자 펄스를 획득하고, 획득된 상기 양자 펄스의 길이 중 상기 기준 펄스 길이보다 짧은 길이를 갖는 양자 펄스에 대한 양자 게이트를 선택하며, 선택된 양자 게이트에 대한 요구 충실도를 조절하여, 조절된 요구 충실도에 따른 양자 펄스를 다시 획득하는 양자 게이트 병합 방법. |

| 20 | 제19항에 있어서, 상기 충실도를 조절하는 단계는 상기 기준 펄스 길이보다 짧은 길이를 갖는 양자 펄스 각각의 길이에 따라 상기 요구 충실도를 차등 조절하는 양자 게이트 병합 방법. |