| 번호 | 청구항 |

|---|---|

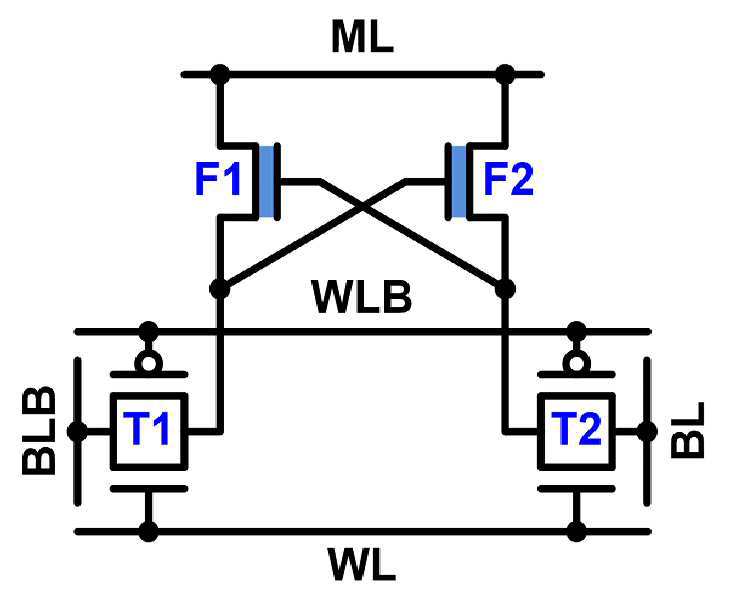

| 1 | 제1 매치라인과 일단이 연결되는 제1 및 제2 FeFET; 및 활성화된 제1 워드라인쌍에 의해 턴온되어 상기 제1 FeFET의 타단과 제1 비트라인쌍의 비트라인바를 전기적으로 연결하는 제1 트랜스미션 게이트와 상기 제2 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인을 전기적으로 연결하는 제2 트랜스미션 게이트를 포함하고, 상기 제1 및 제2 FeFET의 게이트는 상기 제2 및 제1 FeFET의 타단에 크로스 커플 연결되는 CAM 셀. |

| 2 | 제1항에 있어서, 제1 트랜스미션 게이트는 상기 제1 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인바 사이에 연결되고 게이트가 상기 제1 워드라인쌍의 워드라인바에 연결되는 PMOS 트랜지스터와 상기 제1 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인바 사이에 연결되고 게이트가 상기 제1 워드라인쌍의 워드라인에 연결되는 NMOS 트랜지스터를 포함하는 CAM 셀. |

| 3 | 제1항에 있어서, 제2 트랜스미션 게이트는 상기 제2 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인 사이에 연결되고 게이트가 상기 제1 워드라인쌍의 워드라인바에 연결되는 PMOS 트랜지스터와 상기 제2 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인 사이에 연결되고 게이트가 상기 제1 워드라인쌍의 워드라인에 연결되는 NMOS 트랜지스터를 포함하는 CAM 셀. |

| 4 | 제1항에 있어서, 상기 CAM 셀은 라이트 동작에 의해 데이터 "0"이 저장되는 경우 상기 제1 FeFET는 HVT 상태(High VTH State)를 갖고 상기 제2 FeFET는 LVT 상태(Low VTH State)를 가지며, 데이터 "1"이 저장되는 경우 상기 제1 FeFET는 LVT 상태를 갖고 상기 제2 FeFET는 HVT 상태를 갖는 CAM 셀. |

| 5 | 제4항에 있어서, 상기 CAM 셀은 상기 라이트 동작의 제1 단계에서 상기 제1 매치라인으로 LVT보다 낮은 제2 전압이 인가되고, 저장되는 데이터에 따라 상기 제1 비트라인쌍을 통해 인가되는 전압레벨에 의해 상기 제1 및 제2 FET가 LVT 또는 HVT 상태를 갖는 CAM 셀. |

| 18 | 제17항에 있어서, 상기 CAM 셀은 상기 라이트 동작 시에 상기 어드레스에 따라 상기 제1 워드라인쌍이 활성화되면 상기 제1 트랜스미션 게이트와 상기 제2 트랜스미션 게이트가 턴온되어, 상기 제1 FeFET의 타단 및 상기 제2 FeFET의 게이트를 상기 제1 비트라인쌍의 비트라인바와 전기적으로 연결하고, 상기 제2 FeFET의 타단 및 상기 제1 FeFET의 게이트를 상기 제1 비트라인쌍의 비트라인과 전기적으로 연결하는 CAM. |

| 6 | 제5항에 있어서, 상기 제1 트랜스미션 게이트는 상기 라이트 동작의 제1 단계에서 데이터와 함께 인가되는 어드레스에 따라 상기 제1 워드라인쌍의 워드라인으로 HVT보다 높은 제1 전압이 인가되고, 워드라인바로 상기 제2 전압이 인가되어 상기 제1 워드라인쌍이 활성화되면 턴온되어, 상기 제1 FeFET의 타단 및 상기 제2 FeFET의 게이트를 상기 제1 비트라인쌍의 비트라인바와 전기적으로 연결하고, 상기 제2 트랜스미션 게이트는 상기 제1 워드라인쌍이 활성화되면 턴온되어, 상기 제2 FeFET의 타단 및 상기 제1 FeFET의 게이트를 상기 제1 비트라인쌍의 비트라인과 전기적으로 연결하는 CAM 셀. |

| 7 | 제6항에 있어서, 상기 제1 및 제2 FeFET는 상기 CAM 셀에 저장될 데이터에 따라 상기 비트라인바로 상기 제1 전압이 인가되며, 상기 비트라인으로 상기 제2 전압이 인가되면 각각 HVT 및 LVT 상태를 갖고, 상기 비트라인으로 상기 제1 전압이 인가되고, 상기 비트라인바로 상기 제2 전압이 인가되면 각각 LVT 및 HVT 상태를 갖는 CAM 셀. |

| 8 | 제6항에 있어서, 상기 CAM 셀은 "X"(don't care)가 저장될 수 있는 TCAM 셀이고, 데이터 "X"가 저장되는 경우, 상기 라이트 동작의 제2 단계에서 상기 제1 및 제2 FeFET는 모두 HVT 상태(High VTH State)를 갖는 CAM 셀. |

| 9 | 제8항에 있어서, 상기 CAM 셀은 상기 라이트 동작의 제2 단계에서 상기 어드레스에 따라 상기 제1 매치라인으로 상기 제1 전압이 인가되고, 상기 제1 비트라인쌍을 통해 상기 제2 전압이 인가되어 상기 제1 및 제2 FET가 HVT 상태를 갖는 CAM 셀. |

| 10 | 제9항에 있어서, 상기 CAM 셀은 상기 제1 매치라인이 상기 LVT와 상기 HVT 사이의 전압 레벨을 갖는 제3 전압으로 프리차지되는 프리차지 단계와 상기 CAM 셀의 제1 및 제2 FeFET의 상태와 검색될 데이터에 따라 상기 비트라인바 및 상기 비트라인을 통해 인가되는 전압레벨이 서로 매치되지 않으면 프리차지된 상기 제1 매치라인의 전압 레벨이 상기 제2 전압으로 강하되는 검색 단계로 검색 동작이 수행되는 CAM 셀. |

| 11 | 제10항에 있어서, 상기 제1 및 제2 트랜스미션 게이트는 상기 검색 동작 시에 상기 워드라인쌍의 워드라인으로 인가되는 상기 제3 전압과 워드라인바로 인가되는 상기 제2 전압에 의해 턴온되는 CAM 셀. |

| 12 | 제11항에 있어서, 상기 제1 및 제2 FeFET는 상기 프리차지 단계에서 상기 비트라인쌍으로 인가되는 상기 제2 전압에 의해 턴오프되고, 상기 검색 단계에서 상기 제1 및 제2 FeFET 중 LVT 상태를 갖는 FeFET는 게이트가 상기 제1 또는 제2 트랜스미션 게이트 중 하나를 통해 상기 비트라인바 또는 상기 비트라인에 연결되고, 게이트가 연결된 상기 비트라인바 또는 상기 비트라인으로 상기 제3 전압이 인가되면 턴온되어, 제3 전압으로 프리차지된 상기 제1 매치라인과 상기 제2 전압 레벨을 갖는 상기 비트라인바 또는 상기 비트라인을 전기적으로 연결하여 상기 매치라인의 전압레벨을 상기 제2 전압의 레벨로 강하시키는 CAM 셀. |

| 13 | 제1항에 있어서, 상기 제1 및 제2 FeFET는 가변되는 문턱전압(VTH)에서 상대적으로 낮은 문턱전압인 LVT와 상대적으로 높은 문턱전압인 HVT가 모두 양의 전압레벨을 갖는 타입 II FeFET로 구현되는 CAM 셀. |

| 14 | 제1 방향으로 연장되는 다수의 매치라인, 다수의 워드라인쌍과 상기 제1 방향과 수직인 제2 방향으로 연장되는 다수의 비트라인쌍에 의해 정의되는 다수의 CAM 셀; 및 상기 다수의 매치라인 중 대응하는 매치라인에 연결되어, 매치라인을 프리차지하는 다수의 프리차지 회로를 포함하고, 상기 다수의 CAM 셀 각각은 상기 다수의 매치라인 중 제1 매치라인과 일단이 연결되는 제1 및 제2 FeFET; 및 활성화된 제1 워드라인쌍에 의해 턴온되어 상기 제1 FeFET의 타단과 제1 비트라인쌍의 비트라인바를 전기적으로 연결하는 제1 트랜스미션 게이트와 상기 제2 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인을 전기적으로 연결하는 제2 트랜스미션 게이트를 포함하고, 상기 제1 및 제2 FeFET의 게이트는 상기 제2 및 제1 FeFET의 타단에 크로스 커플 연결되는 CAM. |

| 15 | 제14항에 있어서, 제1 트랜스미션 게이트는 상기 제1 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인바 사이에 연결되고 게이트가 상기 제1 워드라인쌍의 워드라인바에 연결되는 PMOS 트랜지스터와 상기 제1 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인바 사이에 연결되고 게이트가 상기 제1 워드라인쌍의 워드라인에 연결되는 NMOS 트랜지스터를 포함하고, 제2 트랜스미션 게이트는 상기 제2 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인 사이에 연결되고 게이트가 상기 제1 워드라인쌍의 워드라인바에 연결되는 PMOS 트랜지스터와 상기 제2 FeFET의 타단과 상기 제1 비트라인쌍의 비트라인 사이에 연결되고 게이트가 상기 제1 워드라인쌍의 워드라인에 연결되는 NMOS 트랜지스터를 포함하는 CAM. |

| 16 | 제14항에 있어서, 상기 CAM 셀은 라이트 동작에 의해 데이터 "0"이 저장되는 경우 상기 제1 FeFET는 HVT 상태(High VTH State)를 갖고 상기 제2 FeFET는 LVT 상태(Low VTH State)를 가지며, 데이터 "1"이 저장되는 경우 상기 제1 FeFET는 LVT 상태를 갖고 상기 제2 FeFET는 HVT 상태를 가지며, 데이터 "X"(don't care)가 저장되는 경우, 상기 제1 및 제2 FeFET는 모두 HVT 상태(High VTH State)를 갖는 CAM. |

| 17 | 제16항에 있어서, 상기 CAM 셀은 상기 라이트 동작의 제1 단계에서 상기 제1 매치라인으로 LVT보다 낮은 제2 전압이 인가되고, 저장되는 데이터에 따라 상기 제1 비트라인쌍을 통해 인가되는 전압레벨에 의해 상기 제1 및 제2 FET가 LVT 또는 HVT 상태를 갖고, 상기 라이트 동작의 제2 단계에서 데이터와 함께 인가되는 어드레스에 따라 상기 제1 매치라인으로 HVT보다 높은 제1 전압이 인가되고, 상기 제1 비트라인쌍을 통해 상기 제2 전압이 인가되어 상기 제1 및 제2 FET가 HVT 상태를 갖는 CAM. |

| 19 | 제18항에 있어서, 상기 제1 및 제2 FeFET는 상기 라이트 동작의 제1 단계에서, 상기 CAM 셀에 저장될 데이터에 따라 상기 비트라인바로 상기 제1 전압이 인가되며, 상기 비트라인으로 상기 제2 전압이 인가되면 각각 HVT 및 LVT 상태를 갖고, 상기 비트라인으로 상기 제1 전압이 인가되고, 상기 비트라인바로 상기 제2 전압이 인가되면 각각 LVT 및 HVT 상태를 갖는 CAM. |

| 20 | 제19항에 있어서, 상기 CAM 셀은 상기 제1 매치라인이 상기 LVT와 상기 HVT 사이의 전압 레벨을 갖는 제3 전압으로 프리차지되는 프리차지 단계와 워드라인으로 상기 제3 전압이 인가되고 워드라인바로 상기 제2 전압이 인가되어 상기 워드라인쌍이 활성화되며, 상기 CAM 셀의 제1 및 제2 FeFET의 상태와 검색될 데이터에 따라 상기 비트라인바 및 상기 비트라인을 통해 인가되는 전압레벨이 서로 매치되지 않으면 프리차지된 상기 제1 매치라인의 전압 레벨이 상기 제2 전압으로 강하되는 검색 단계로 검색 동작이 수행되는 CAM. |