| 번호 | 청구항 |

|---|---|

| 15 | 제13항에 있어서, 상기 다수의 메모리 셀 각각은 데이터 "0"이 저장되는 경우 상기 제1 SR-FTJ는 고저항 상태(High Resistance State: HRS)를 갖고 상기 제2 SR-FTJ는 저저항 상태(Low Resistance State: LRS)를 가지며, 데이터 "1"이 저장되는 경우 상기 제1 SR-FTJ는 저저항 상태 갖고 상기 제2 SR-FTJ는 고저항 상태를 갖는 메모리 장치의 동작 방법. |

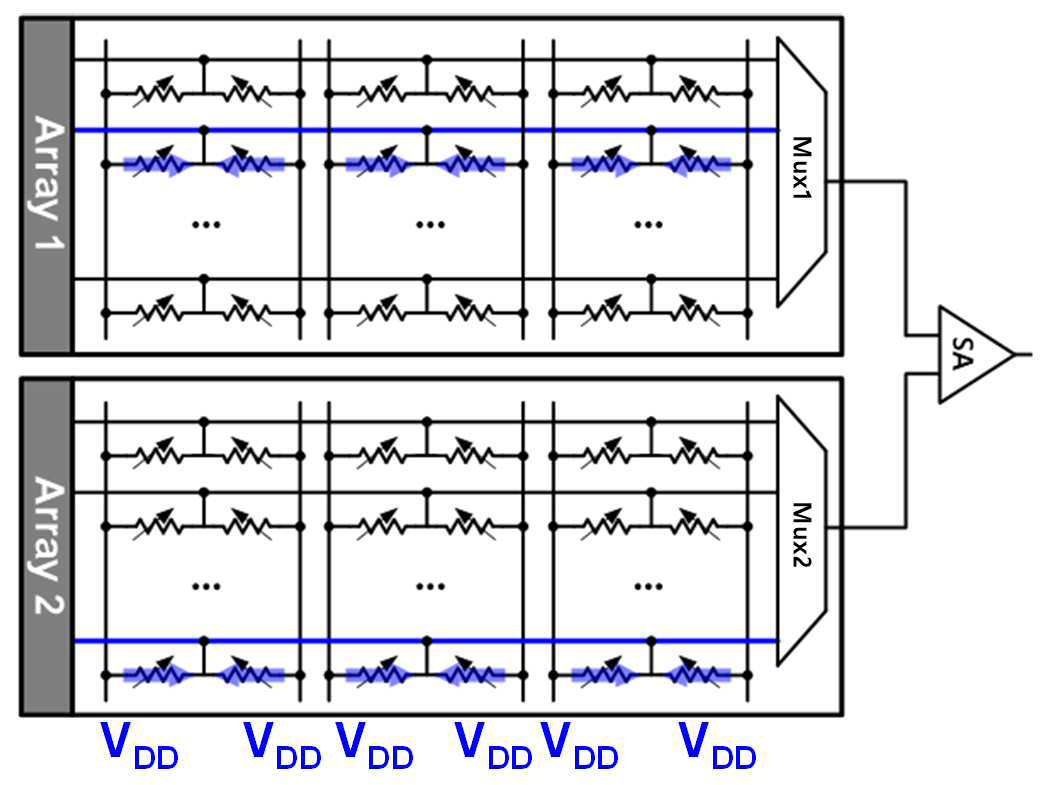

| 1 | 제1 방향으로 연장되는 다수의 매치라인과 제1 방향과 교차하는 제2 방향으로 연장되는 다수의 서치라인쌍 사이에 각각 연결되는 2개의 자기-정류 강유전체 터널 접합 소자(Self-rectifying Ferroelectric Tunnel Junction Element: 이하 SR-FTJ)로 구성되는 다수의 메모리 셀; 상기 다수의 매치라인과 상기 다수의 서치라인쌍으로 동작 상태에 따른 전압을 공급하는 전원 공급부; 및 CAM(Content Addressable Memory) 모드와 PUF(Physically Unclonable Function) 모드 중 상기 PUF 모드로 동작 시에 챌린지로서 전송된 주소에 따라 선택되는 매치라인에 연결된 다수의 메모리 셀 각각의 2개의 SR-FTJ에 역방향 전압이 인가되어 발생하는 누설 전류에 의해, 선택된 매치라인에 발생되는 전압 변화를 감지 증폭하여 상기 챌린지에 대응하는 응답을 생성하는 PUF 응답 생성부를 포함하는 메모리 장치. |

| 2 | 제1항에 있어서, 상기 다수의 메모리 셀 각각은 상기 다수의 매치라인 중 대응하는 매치라인과 상기 다수의 서치라인쌍 중 대응하는 서치라인쌍의 서치라인 사이에 연결되는 제1 SR-FTJ; 및 상기 다수의 매치라인 중 대응하는 매치라인과 상기 다수의 서치라인쌍 중 대응하는 서치라인쌍의 서치라인바 사이에 연결되는 제2 SR-FTJ를 포함하는 메모리 장치. |

| 3 | 제2항에 있어서, 상기 응답 생성부는 상기 다수의 매치라인 중 서로 다른 기지정된 개수의 매치라인과 연결되어 상기 챌린지에 대응하는 매치라인을 선택하는 다수의 먹스; 및 상기 다수의 먹스 중 대응하는 2개의 먹스가 각각 선택한 매치라인 사이의 전압 차를 감지 증폭하여 상기 응답을 생성하는 적어도 하나의 센스 앰프를 포함하는 메모리 장치. |

| 4 | 제3항에 있어서, 상기 전원 공급부는 디스차지 단계 및 응답 생성 단계로 구분되어 동작하는 상기 PUF 모드의 상기 디스차지 단계에서 상기 다수의 매치라인과 상기 다수의 서치라인쌍이 디스차지되도록 접지 전압 레벨을 인가하고, 상기 응답 생성 단계에서 상기 다수의 매치라인 중 상기 챌린지에 의해 지정된 주소에 따라 선택된 매치라인에는 인가되는 전압을 차단하여 플로팅시키고, 나머지 매치라인과 상기 서치라인쌍으로는 기지정된 전압 레벨의 전원 전압을 인가하는 메모리 장치. |

| 5 | 제4항에 있어서, 상기 적어도 하나의 센스 앰프는 상기 응답 생성 단계에서 상기 다수의 먹스 중 대응하는 2개의 먹스가 각각 상기 챌린지에 의해 지정된 주소에 따라 매치라인을 선택하여 연결하면, 선택된 2개의 매치라인에 연결된 다수의 메모리 셀 각각에서 2개의 SR-FTJ에 역방향 전압이 인가되어 발생하는 누설 전류에 의해 변화하는 매치라인 사이의 전압 차를 감지 증폭하여 상기 응답을 생성하는 메모리 장치. |

| 6 | 제4항에 있어서, 상기 다수의 메모리 셀 각각은 라이트 동작과 검색 동작으로 구분되어 동작하는 상기 CAM 모드의 상기 라이트 동작에 의해 데이터 "0"이 저장되는 경우 상기 제1 SR-FTJ는 고저항 상태(High Resistance State: HRS)를 갖고 상기 제2 SR-FTJ는 저저항 상태(Low Resistance State: LRS)를 가지며, 데이터 "1"이 저장되는 경우 상기 제1 SR-FTJ는 저저항 상태 갖고 상기 제2 SR-FTJ는 고저항 상태를 갖는 메모리 장치. |

| 7 | 제6항에 있어서, 상기 전원 공급부는 상기 라이트 동작의 고저항 설정 단계에서 다수의 매치라인 중 인가된 주소에 따라 선택되는 매치라인으로 상기 접지 전압을 인가하고, 나머지 매치라인으로는 기지정된 전압 레벨의 라이트 전압의 1/2 레벨의 전압을 인가하며, 상기 다수의 서치라인쌍 각각에는 대응하는 메모리 셀(MC)에 저장되어야 하는 데이터에 따른 전압을 인가하고, 상기 라이트 동작의 저저항 설정 단계에서는 선택되는 매치라인으로 상기 라이트 전압을 인가하고, 나머지 매치라인과 상기 다수의 서치라인쌍으로는 상기 고저항 설정 단계에서 인가되는 전압을 유지하는 메모리 장치. |

| 8 | 제7항에 있어서, 상기 전원 공급부는 상기 CAM 모드의 라이트 동작 시, 메모리 셀에 저장되어야 하는 데이터가 "0"이면, 대응하는 서치라인쌍에서 서치라인으로는 상기 라이트 전압을 인가하고, 서치라인바로는 상기 접지 전압을 인가하며, 메모리 셀에 저장되어야 하는 데이터가 "1"이면, 대응하는 서치라인쌍에서 서치라인으로는 상기 접지 전압을 인가하고, 서치라인바로는 상기 라이트 전압을 인가하는 메모리 장치. |

| 9 | 제6항에 있어서, 상기 전원 공급부는 상기 검색 동작의 프리차지 단계에서 상기 다수의 매치라인과 상기 다수의 서치라인쌍으로 상기 전원 전압을 인가하여 프리차지하고, 상기 검색 동작의 매치 평가 단계에서는 상기 다수의 매치라인으로 인가되는 전원을 차단하여 플로팅 시키고, 상기 다수의 서치라인쌍으로 검색하고자 하는 데이터에 대응하는 전압을 인가하는 메모리 장치. |

| 10 | 제9항에 있어서, 상기 전원 공급부는 상기 검색 동작 시에 검색되야 하는 데이터가 "0"이면, 대응하는 서치라인쌍에서 서치라인으로는 상기 접지 전압을 인가하고, 서치라인바로는 상기 전원 전압을 인가하며, 검색되야 하는 데이터가 "1"이면, 대응하는 서치라인쌍에서 서치라인으로는 상기 전원 전압을 인가하고, 서치라인바로는 상기 접지 전압을 인가하는 메모리 장치. |

| 11 | 제1항에 있어서, 상기 다수의 메모리 셀은 상기 다수의 서치라인쌍 각각의 서치라인과 서치라인바가 상기 다수의 매치 라인의 상부 및 하부에 각각 배치되고, 상기 2개의 SR-FTJ는 대응하는 매치라인과 서치라인 사이 및 대응하는 매치라인과 서치라인바 사이에 적층된 3D 구조로 구현되는 메모리 장치. |

| 12 | 제1 방향으로 연장되는 다수의 매치라인과 제1 방향과 교차하는 제2 방향으로 연장되는 다수의 서치라인쌍 사이에 각각 연결되는 2개의 자기-정류 강유전체 터널 접합 소자(Self-rectifying Ferroelectric Tunnel Junction Element: 이하 SR-FTJ)로 구성되는 다수의 메모리 셀을 포함하는 메모리 장치의 동작 방법에 있어서, 인가되는 명령에 따라 CAM 모드 또는 PUF 모드의 동작 모드를 판별하는 단계; 판별된 동작 모드가 상기 PUF 모드이면, 챌린지로서 전송된 주소에 따라 선택되는 매치라인에 연결된 다수의 메모리 셀 각각의 2개의 SR-FTJ에 역방향 전압이 인가되어 발생하는 누설 전류에 의해, 선택된 매치라인에 발생되는 전압 변화를 감지 증폭하여 상기 챌린지에 대응하는 응답을 생성하는 단계를 포함하는 메모리 장치의 동작 방법. |

| 13 | 제12항에 있어서, 상기 다수의 메모리 셀 각각은 상기 다수의 매치라인 중 대응하는 매치라인과 상기 다수의 서치라인쌍 중 대응하는 서치라인쌍의 서치라인 사이에 연결되는 제1 SR-FTJ; 및 상기 다수의 매치라인 중 대응하는 매치라인과 상기 다수의 서치라인쌍 중 대응하는 서치라인쌍의 서치라인바 사이에 연결되는 제2 SR-FTJ를 포함하는 메모리 장치의 동작 방법. |

| 14 | 제13항에 있어서, 상기 응답을 생성하는 단계는 상기 다수의 매치라인과 상기 다수의 서치라인쌍으로 접지 전압을 인가하여 디스차지시키는 단계; 상기 다수의 매치라인 중 상기 챌린지에 의해 지정된 주소에 따라 선택된 매치라인에는 인가되는 전압을 차단하여 플로팅시키고, 나머지 매치라인과 상기 서치라인쌍으로는 기지정된 전압 레벨의 전원 전압을 인가하는 단계; 및 상기 챌린지에 의해 지정된 주소에 따라 매치라인을 선택하고, 상기 응답을 생성하기 위해 선택된 2개의 매치라인에 연결된 다수의 메모리 셀 각각에서 2개의 SR-FTJ에서 발생하는 누설 전류에 의해 변화하는 선택된 매치라인 사이의 전압 차를 감지 증폭하는 단계를 포함하는 메모리 장치의 동작 방법. |

| 16 | 제15항에 있어서, 상기 메모리 장치의 동작 방법은 판별된 동작 모드가 상기 CAM 모드이면, 라이트 명령 또는 검색 명령이 인가되는지 판별하는 단계; 상기 라이트 명령이 인가되면, 상기 다수의 메모리 셀 중 라이트 명령과 함께 인가된 주소에 따른 메모리 셀에 인가된 데이터를 라이트하는 단계; 및 상기 검색 명령이 인가되면, 검색 명령과 함께 인가된 데이터가 저장된 메모리 셀을 검색하는 단계를 포함하는 메모리 장치의 동작 방법. |

| 17 | 제16항에 있어서, 상기 라이트하는 단계는 다수의 매치라인 중 인가된 주소에 따라 선택되는 매치라인으로 접지 전압을 인가하고, 나머지 매치라인으로는 기지정된 전압 레벨의 라이트 전압의 1/2 레벨의 전압을 인가하며, 상기 다수의 서치라인쌍 각각에는 대응하는 메모리 셀(MC)에 저장되어야 하는 데이터에 따른 전압을 인가하는 고저항 설정 단계; 및 선택되는 매치라인으로 상기 라이트 전압을 인가하고, 나머지 매치라인과 상기 다수의 서치라인쌍으로는 상기 고저항 설정 단계에서 인가되는 전압을 유지하는 저저항 설정 단계를 포함하는 메모리 장치의 동작 방법. |

| 18 | 제17항에 있어서, 상기 라이트하는 단계는 메모리 셀에 저장되어야 하는 데이터가 "0"이면, 대응하는 서치라인쌍에서 서치라인으로는 상기 라이트 전압을 인가하고, 서치라인바로는 상기 접지 전압을 인가하며, 메모리 셀에 저장되어야 하는 데이터가 "1"이면, 대응하는 서치라인쌍에서 서치라인으로는 상기 접지 전압을 인가하고, 서치라인바로는 상기 라이트 전압을 인가하는 메모리 장치의 동작 방법. |

| 19 | 제16항에 있어서, 상기 검색하는 단계는 상기 다수의 매치라인과 상기 다수의 서치라인쌍으로 기지정된 전압 레벨의 전원 전압을 인가하여 프리차지하는 단계; 및 상기 다수의 매치라인으로 인가되는 전원을 차단하여 플로팅 시키고, 상기 다수의 서치라인쌍으로 검색하고자 하는 데이터에 대응하는 전압을 인가하여, 인가된 데이터에 대응하는 데이터가 저장된 메모리 셀이 연결된 매치라인의 전압이 강하되도록 하는 매치 평가 단계를 포함하는 메모리 장치의 동작 방법. |

| 20 | 제19항에 있어서, 상기 검색하는 단계는 검색되야 하는 데이터가 "0"이면, 대응하는 서치라인쌍에서 서치라인으로는 접지 전압을 인가하고, 서치라인바로는 상기 전원 전압을 인가하며, 검색되야 하는 데이터가 "1"이면, 대응하는 서치라인쌍에서 서치라인으로는 상기 전원 전압을 인가하고, 서치라인바로는 상기 접지 전압을 인가하는 메모리 장치의 동작 방법. |