| 번호 | 청구항 |

|---|---|

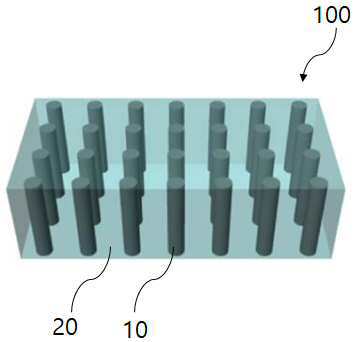

| 1 | 스트레처블 전자 소자(stretchable electronic device)에 있어서,반도체 재료를 포함하는 복수의 3차원 마이크로 기둥이 배열되는 기둥 어레이; 상기 기둥 어레이를 전체적으로 매립하는 엘라스토머를 포함하는 페시베이션 층;상기 기둥 어레이의 상부면에 형성된 가요성을 갖는 상부 전극; 및상기 기둥 어레이의 하부면에 형성된 가요성을 갖는 하부 전극을 포함하고,상기 상부 전극 및 상기 하부 전극 각각은 나노 와이어 네트워크 구조를 포함하고,상기 3차원 마이크로 기둥은 기둥 형상을 갖는 무기 물질의 제 1 반도체층; 및 상기 제 1 반도체층의 표면 상에 형성되는 유기 물질의 제 2 반도체층을 포함하는,스트레처블 전자 소자. |

| 2 | 제 1 항에 있어서,외부로부터 스트레인이 인가되는 경우에, 인가된 스트레인은 상기 페시베이션 층에 흡수되어, 상기 기둥 어레이에 기계적 결함이 발생하는 것이 방지되는 스트레처블 전자 소자. |

| 3 | 제 1 항에 있어서,상기 3차원 마이크로 기둥간 간격에 따라 상기 스트레처블 전자 소자의 신축성이 제어되는 스트레처블 전자 소자. |

| 4 | 삭제 |

| 5 | 제 1 항에 있어서,상기 상부 전극 및 상기 하부 전극은 Fe, Ag, Au, Cu, Cr, W, Al, Mo, Zn, Ni, Pt, Pd, Co, In, Mn, Si, Ta, Ti, Sn, Pb, V, Ru, Ir, Zr, Rh 및 Mg 중에서 선택되는 하나 이상으로 형성되는 스트레처블 전자 소자. |

| 6 | 삭제 |

| 7 | 제 1 항에 있어서,상기 스트레처블 전자 소자는 100% 이상 스트레칭 가능한 스트레처블 전자 소자. |

| 8 | 제 1 항에 있어서,상기 기둥 어레이의 하부면과 상기 하부 전극 사이에 형성된 Ti 및 Ag를 포함하는 버퍼층을 더 포함하는 스트레처블 전자 소자. |

| 9 | 제 1 항에 있어서,상기 제 1 반도체층은 Si, GaAs, ZnO 및 TiO2 중 하나 이상을 포함하는 스트레처블 전자 소자. |

| 10 | 제 1 항에 있어서,상기 제 2 반도체층은 PEDOT:PSS, P3HT, PCDTBT, PCTDTBT, MEH-PPV, PTB7, PBDTTT-CF, PFN, PCBM, 및 ICBA 중 하나 이상을 포함하는 스트레처블 전자 소자. |

| 11 | 제 1 항에 있어서, 상기 스트레처블 전자 소자는 태양 전지, 트랜지스터, 에너지 하베스팅 소자 및 센서 중 어느 하나인 스트레처블 전자 소자. |

| 12 | 제 1 항에 있어서,상기 페시베이션 층은 PDMS(Polydimethylsiloxane), 에코플렉스(Ecoflex), 하이드로겔(hydrogel), PEBA(polyether block amides) 및 EVA(ethylene-vinyl acetate) 중 적어도 하나를 포함하는 스트레처블 전자 소자. |

| 13 | 스트레처블 전자 소자의 제조 방법에 있어서,반도체 재료를 포함하는 복수의 3차원 마이크로 기둥이 배열되는 기둥 어레이를 형성하는 기둥 어레이 형성 단계; 엘라스토머를 포함하는 페시베이션 층에 의해 상기 기둥 어레이를 전체적으로 매립하는 매립 단계;상기 기둥 어레이의 상부면에 가요성을 갖는 상부 전극을 형성하는 상부 전극 형성 단계; 및상기 기둥 어레이의 하부면에 가요성을 갖는 하부 전극을 형성하는 하부 전극 형성 단계를 포함하고,상기 상부 전극 및 상기 하부 전극 각각은 나노 와이어 네트워크 구조를 포함하도록 형성하고,상기 기둥 어레이 형성 단계는 기둥 형상을 갖는 무기 물질의 제 1 반도체층을 형성하는 단계; 및 상기 제 1 반도체층의 표면 상에 유기 물질의 제 2 반도체층을 형성하는 단계를 포함하는,스트레처블 전자 소자의 제조 방법. |

| 14 | 삭제 |

| 15 | 제 13 항에 있어서,상기 상부 전극 형성 단계는, Fe, Ag, Au, Cu, Cr, W, Al, Mo, Zn, Ni, Pt, Pd, Co, In, Mn, Si, Ta, Ti, Sn, Pb, V, Ru, Ir, Zr, Rh 및 Mg 중에서 선택되는 하나 이상의 재료를 상기 기둥 어레이의 상부면에 형성하는 단계를 포함하는 스트레처블 전자 소자의 제조 방법. |

| 16 | 제 13 항에 있어서,상기 하부 전극 형성 단계는, 상기 기둥 어레이의 하부면에 Ti 및 Ag를 포함하는 버퍼층을 형성하는 단계; 및상기 버퍼층 상에 Fe, Ag, Au, Cu, Cr, W, Al, Mo, Zn, Ni, Pt, Pd, Co, In, Mn, Si, Ta, Ti, Sn, Pb, V, Ru, Ir, Zr, Rh 및 Mg 중에서 선택되는 하나 이상의 재료를 형성하는 단계를 포함하는 스트레처블 전자 소자의 제조 방법. |

| 17 | 제 13 항에 있어서,상기 기둥 어레이는 촉매 금속 에칭(metal-assisted chemical etching)에 의해 형성되는 스트레처블 전자 소자의 제조 방법. |

| 18 | 제 13 항에 있어서,상기 매립 단계는 PDMS(Polydimethylsiloxane), 에코플렉스(Ecoflex), 하이드로겔(hydrogel), PEBA(polyether block amides) 및 EVA(ethylene-vinyl acetate) 중 적어도 하나에 의해 상기 기둥 어레이를 매립하는 스트레처블 전자 소자의 제조 방법. |