| 번호 | 청구항 |

|---|---|

| 7 | 제6항에 있어서, 상기 제2 덧셈기와 상기 8x16 블록 SAD를 출력하는 제3 덧셈기 사이에는 소정 개수의 제2 딜레이 유닛이 제공되며, 상기 제3 덧셈기는 제2 딜레이 유닛에 의해 2 클럭 사이클 지연된 8x8 블록 SAD와 현재 상기 제2 덧셈기에서 출력하는 8x8 블록 SAD를 조합하여 8x16 블록 SAD를 출력하는 움직임 추정 장치. |

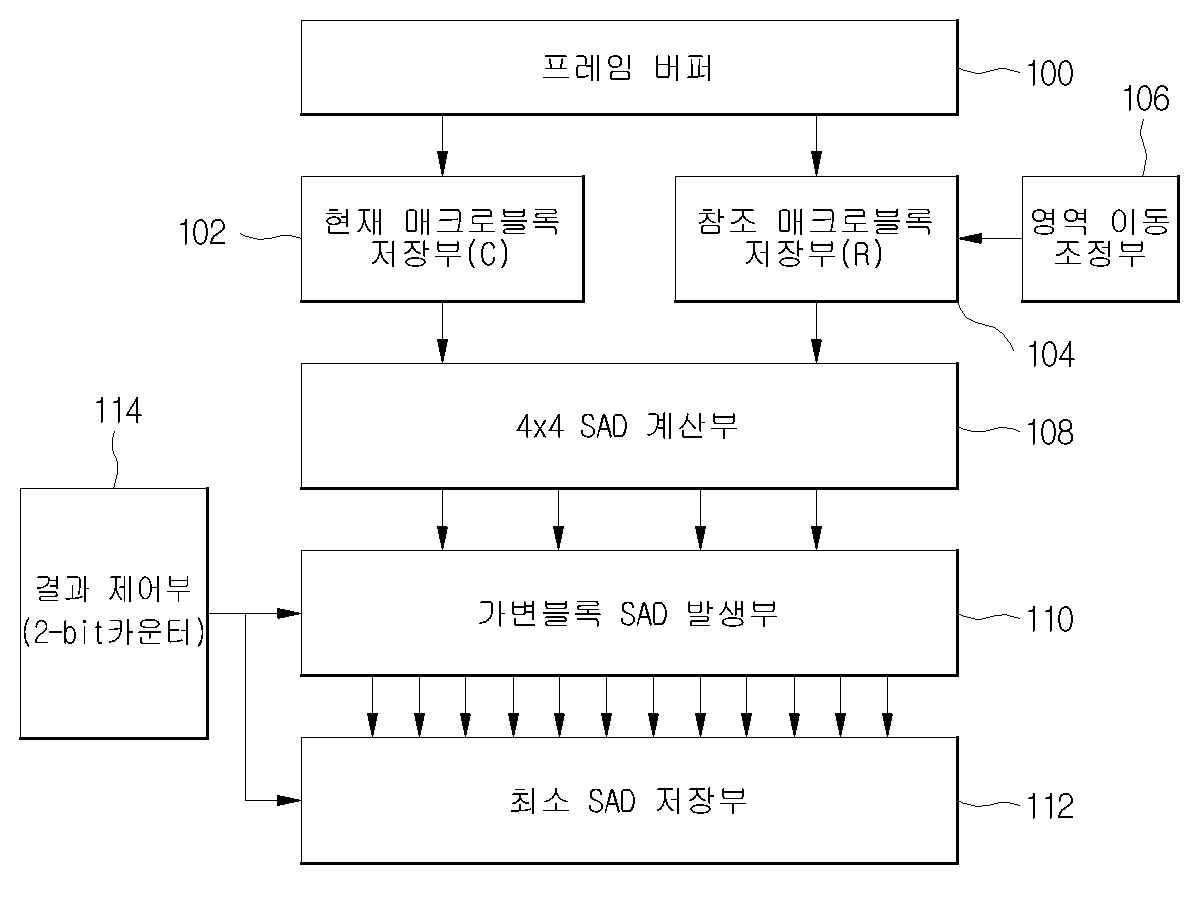

| 1 | 가변 블록을 이용한 전역 탐색 움직임 추정 장치에 있어서, 매 클럭 사이클마다 현재 프레임의 매크로블록 및 참조 프레임의 매크로블록의 4x4 블록에 대한 SAD를 미리 설정된 개수만큼 계산하는 4x4 SAD 계산부;n 클럭 사이클-상기 n 클럭 사이클은 상기 현재 및 참조 매크로블록에 대한 최초 4x4 블록 SAD가 입력되는 시점에 해당됨-부터 상기 4x4 SAD 계산부에서 계산된 4x4 블록 SAD를 출력하며, n+1 클럭 사이클부터 상기 4x4 블록 SAD를 조합하여 8x4 및 4x8 블록 SAD 중 적어도 하나를 출력하는 제1 덧셈기, n+2 클럭 사이클부터 상기 8x4 및 4x8 블록 SAD를 조합하여 8x8 블록 SAD를 출력하는 제2 덧셈기 및 상기 제2 덧셈기에서 미리 설정된 개수의 8x8 블록 SAD가 출력되는 클럭 사이클에 16x8, 8x16 및 16x16 블록 SAD를 중 적어도 하나를 출력하는 제3 덧셈기를 포함하는 가변 블록 SAD 발생부; 및상기 가변 블록 SAD 발생부에서 생성된 가변 블록 SAD를 기 저장된 대응 가변 블록 SAD와 비교하여 최소 SAD를 저장하는 최소 SAD 저장부를 포함하는 가변 블록을 이용한 움직임 추정 장치. |

| 2 | 제1항에 있어서, 상기 현재 매크로블록 및 참조 매크로블록은 16x16 블록으로 이루어지며, 상기 4x4 SAD 계산부는 4개의 1차원 어레이를 포함하여 매 클럭 사이클마다 4개의 4x4 블록 SAD를 계산하여 출력하는 움직임 추정 장치. |

| 3 | 제2항에 있어서, 상기 1차원 어레이는 16개의 프로세싱 단위 유닛(PE)을 포함하며, 단일 클럭 사이클에 4x4 블록에 포함되는 16개의 픽셀 휘도 차이 절대값을 합산하여 4x4 블록 SAD를 계산하는 움직임 추정 장치. |

| 4 | 제2항에 있어서,상기 제1 덧셈기는 상기 4x4 SAD 계산부에서 계산된 4개의 4x4 블록 SAD를 가로 방향으로 조합하여 8x4 블록 SAD를 출력하며, 세로 방향으로 조합하여 4x8 블록 SAD를 출력하는 움직임 추정 장치. |

| 5 | 제4항에 있어서,상기 제2 덧셈기는 4x4 블록 SAD를 가로 방향으로 조합하는 제1 덧셈기로부터 하나 이상의 8x4 블록 SAD를 수신하고, 이를 조합하여 8x8 블록 SAD를 출력하는 움직임 추정 장치. |

| 6 | 제1항에 있어서, 상기 제2 덧셈기로부터 출력되는 8x8 블록 SAD가 상기 제3 덧셈기로 입력되는 시간을 지연시키는 소정 개수의 딜레이 유닛을 더 포함하되,상기 제2 덧셈기와 상기 16x8 블록 SAD를 출력하는 제3 덧셈기 사이에는 제1 딜레이 유닛이 제공되며, 상기 제3 덧셈기는 제1 딜레이 유닛에 의해 1 클럭 사이클 지연된 8x8 블록 SAD와 현재 상기 제2 덧셈기에서 출력하는 8x8 블록 SAD를 조합하여 16x8 블록 SAD를 출력하는 움직임 추정 장치. |

| 8 | 제6항에 있어서, 상기 제2 덧셈기와 상기 16x16 블록 SAD를 출력하는 제3 덧셈기 사이에는 상기 제3 덧셈기에서 궤환되는 소정 개수의 8x8 블록 SAD이 합산된 결과값을 입력 받아 지연시키는 제3 딜레이 유닛이 제공되며, 상기 제3 덧셈기는 3 클럭 사이클 동안 8x8 블록 SAD를 조합한 결과값과 현재 상기 제2 덧셈기에서 출력하는 8x8 블록 SAD를 조합하여 16x16 블록 SAD를 출력하는 움직임 추정 장치. |

| 9 | 제8항에 있어서, 상기 가변 블록 SAD 발생부 및 최소 SAD 저장부는 2 비트 카운터에 의해 제어되며, 상기 2 비트 카운터에 의해 상기 제3 딜레이 유닛은 4 클럭 사이클마다 초기화되는 움직임 추정 장치. |

| 10 | 제1항에 있어서, 상기 최소 SAD 저장부는 디먹스를 포함하며, 상기 디먹스는 상기 가변 블록 SAD 발생부가 출력하는 가변 블록에 대한 SAD를 상기 가변 블록에 대해 할당된 저장 공간에 배치하는 움직임 추정 장치. |

| 11 | 가변 블록을 이용한 전역 탐색 움직임 추정 방법에 있어서, 매 클럭 사이클마다 현재 프레임의 매크로블록 및 참조 프레임의 매크로블록의 4x4 블록에 대한 SAD를 미리 설정된 개수만큼 계산하는 단계(a);n 클럭 사이클-상기 n 클럭 사이클은 상기 현재 및 참조 매크로블록에 대한 최초 4x4 블록 SAD가 입력되는 시점에 해당됨-부터 상기 계산된 4x4 블록 SAD를 출력하는 단계(b);n+1 클럭 사이클부터 상기 4x4 블록 SAD를 조합하여 8x4 및 4x8 블록 SAD를 출력하는 단계(c);n+2 클럭 사이클부터 상기 8x4 및 4x8 블록 SAD를 조합하여 8x8 블록 SAD 중 적어도 하나를 출력하는 단계(d);상기 (d) 단계에서 미리 설정된 개수의 8x8 블록 SAD가 출력되는 클럭 사이클에 16x8, 8x16 및 16x16 블록 SAD를 중 적어도 하나를 출력하는 단계(e); 및상기 출력된 가변 블록에 대한 SAD를 기 저장된 대응 가변 블록 SAD와 비교하여 최소 SAD를 저장하는 단계(f)를 포함하는 움직임 추정 방법. |

| 12 | 제11항에 있어서, 상기 현재 매크로블록 및 참조 매크로블록은 16x16 블록으로 이루어지며, 상기 (a) 단계는 매 클럭 사이클마다 4개의 4x4 블록 SAD를 계산하여 출력하는 움직임 추정 방법. |

| 13 | 제12항에 있어서상기 (a) 단계는 단일 클럭 사이클에 상기 현재 및 참조 매크로블록의 4x4 블록에 포함되는 16개의 픽셀 휘도 차이 절대값을 합산하여 4x4 블록 SAD를 계산하는 움직임 추정 방법. |

| 14 | 제12항에 있어서상기 (c) 단계는 상기 계산된 4개의 4x4 블록 SAD를 가로 방향으로 조합하여 8x4 블록 SAD를 출력하며, 세로 방향으로 조합하여 4X8 블록 SAD를 출력하는 움직임 추정 방법. |

| 15 | 제14항에 있어서상기 (d) 단계는 상기 (c) 단계에서 출력하는 하나 이상의 8x4 블록 SAD를 수신하고, 이를 조합하여 8x8 블록 SAD를 출력하는 움직임 추정 방법. |

| 16 | 제11항에 있어서상기 (d) 단계에서 출력되는 8x8 블록 SAD를 소정 클럭 사이클 지연시키는 단계(g)를 더 포함하되, 상기 (e) 단계는 1 클럭 사이클 지연된 8x8 블록 SAD와 현재 상기 (d) 단계에서 출력하는 8x8 블록 SAD를 조합하여 16x8 블록 SAD를 출력하는 움직임 추정 방법. |

| 17 | 제16항에 있어서,상기 (e) 단계는 2 클럭 사이클 지연된 8x8 블록 SAD와 현재 상기 (d) 단계에서 출력하는 8x8 블록 SAD를 조합하여 8x16 블록 SAD를 출력하는 움직임 추정 방법. |

| 18 | 제16항에 있어서,상기 (g) 단계는 상기 (e) 단계로부터 궤환되는 소정 개수의 8x8 블록 SAD이 합산된 결과값을 입력 받아 지연시키며, 상기 (e) 단계는 3 클럭 사이클 동안 8x8 블록 SAD를 조합한 결과값과 현재 상기 (d) 단계에서 출력하는 8x8 블록 SAD를 조합하여 16x16 블록 SAD를 출력하는 움직임 추정 방법. |

| 19 | 제11항에 있어서,상기 (b) 단계 내지 (f) 단계는 2 비트 카운터에 의해 제어되며, 상기 2 비트 카운터에 의해 상기 (e) 단계는 4 클럭 사이클마다 초기화과정을 수행하면서 16x16 블록 SAD를 출력하는 움직임 추정 방법. |

| 20 | 제11항에 있어서,상기 (f) 단계는 상기 (b) 단계 내지 (e) 단계에서 출력하는 가변 블록에 대한 SAD를 디먹싱(demuxing)하여 상기 가변 블록에 대해 할당된 저장 공간에 배치하는 움직임 추정 방법. |