| 번호 | 청구항 |

|---|---|

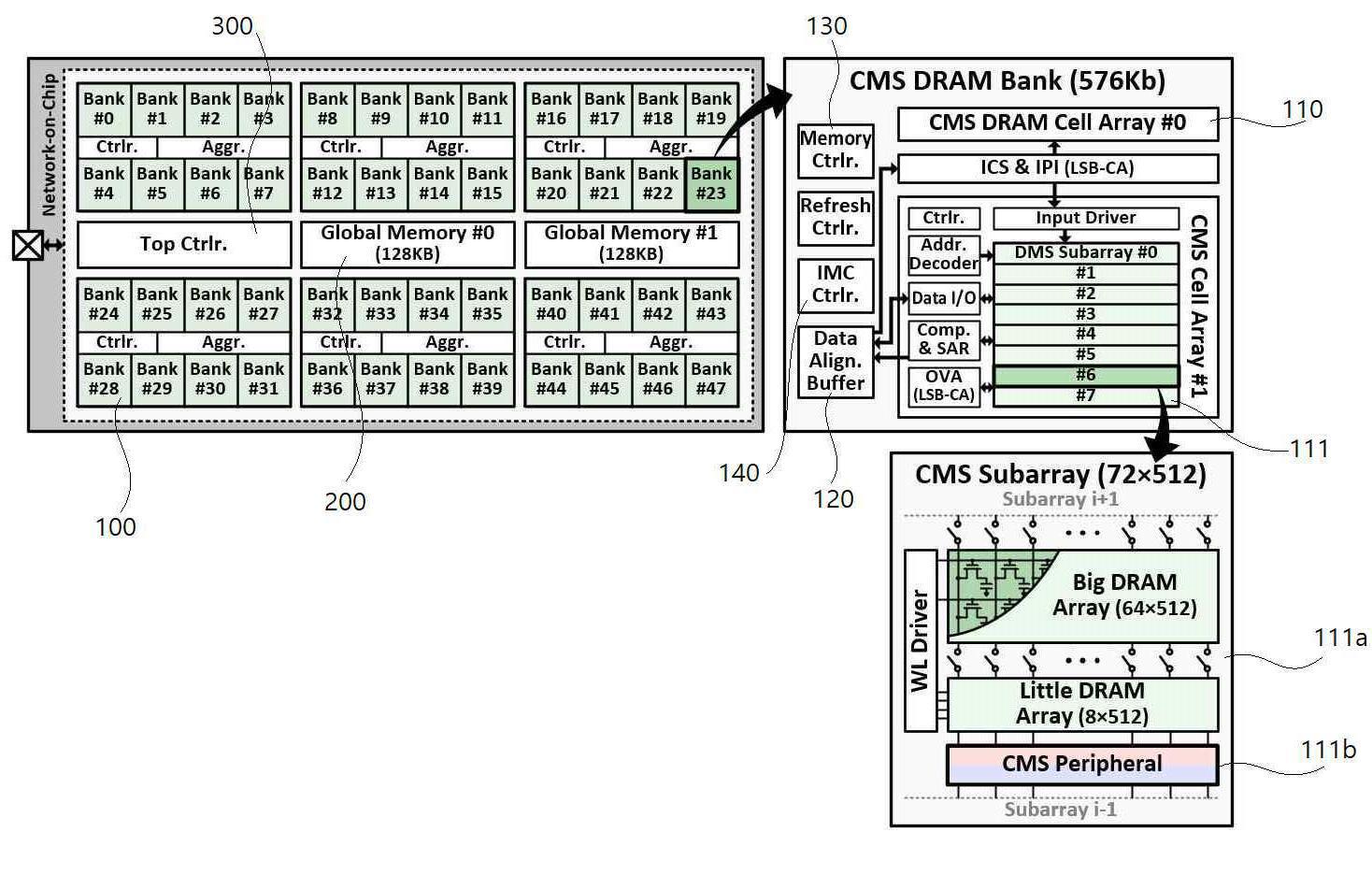

| 1 | 한 쌍의 셀 어레이, 데이터 공급 로직, 그리고 메모리 및 인메모리 컴퓨팅(IMC)를 위한 컨트롤러로 구성되고 소정 용량의 DRAM을 포함하여 메모리로써 데이터를 저장하거나 메모리 내 연산을 수행하는 복수의 DRAM 뱅크; 오프칩 메모리와 데이터를 주고받을 때 데이터를 일시적으로 저장하는 전역 SRAM; 및 상기 오프칩 메모리와 DRAM 뱅크, 또는 서로 다른 DRAM 뱅크 간 데이터 이동을 조절하고, 연산 인스트럭션을 디코딩하여 각 DRAM 뱅크에 전달하는 최상위 컨트롤러;를 포함하고,상기 셀 어레이는 복수의 서브어레이를 포함하며, 상기 서브어레이는 빅 어레이와 리틀 어레이로 구성된 DRAM 어레이, 그리고 연산을 수행하는 연산회로;를 포함하되,상기 연산회로는 비트라인 전압차이를 증폭하는 감지 증폭기; 및 MAC 연산 및 SIMD 연산을 위한 CMSU;를 포함하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 2 | 제 1항에 있어서, 상기 연산회로는 입력 피연산자 선택, 피연산자의 논리 연산, 출력 저장 여부 선택, MAC 연산 또는 아날로그-디지털 컨버터 동작 선택을 수행하는 트랜지스터와 연산 커패시터가 연결된 멀티플렉서로 구성된 8T1C의 회로구조를 갖는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 3 | 제 2항에 있어서,상기 커패시터는 커패시턴스 결합 방식의 MAC 연산 및 연속 근사 레지스터(SAR) ADC의 디지털-아날로그 컨버터(DAC) 동작을 모두 수행하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 4 | 제 2항에 있어서,상기 멀티플렉서는 상기 입력 피연산자 선택을 위해 메모리 어레이 외부의 입력 또는 인접한 연산회로의 출력 중 하나의 피연산자를 선택하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 5 | 제 2항에 있어서, 상기 멀티플렉서는상기 피연산자의 논리 연산을 위해 선택 신호를 비트라인 및 비트라인바에서 받아 피연산자 A로 사용하고, 두 개의 입력 신호를 피연산자 B의 비트, 피연산자 B 반전된 비트, GND, VDD 중 하나로 받아 피연산자 A와 B 사이에서 16가지의 논리 연산을 수행하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 6 | 제 2항에 있어서, 상기 멀티플렉서는상기 출력 저장 여부 선택을 위해 상기 피연산자의 논리 연산을 위한 멀티플렉서의 출력 비트를 상기 커패시터에 저장하였다가 비트라인에 전하 공유를 하고 상기 감지 증폭기(SWSA)를 동작시켜 메모리 쓰기 동작을 수행하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 7 | 제 1항에 있어서,상기 감지 증폭기(SWSA)는비트라인과 비트라인바의 전압차 증폭을 위한 N-MOSFET과 P-MOSFET; 및상기 비트라인 또는 비트라인바 선택을 위한 추가 N-MOSFET과 추가 P-MOSFET;를 갖는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 8 | 제 7항에 있어서,상기 감지 증폭기는 차동 감지 모드 및 직접 감지 모드 중 하나로 선택적으로 동작할 수 있는 재구성 가능한 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 9 | 제 8항에 있어서,상기 차동 감지 모드에서는 상기 감지 증폭기의 비트라인 또는 비트라인바 선택을 위한 2개의 N-MOSFET 및 2개의 P-MOSFET이 모두 켜져서 비트라인 전압 차이를 증폭하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 10 | 제 8항에 있어서, 상기 직접 감지 모드에서는 비트라인 또는 비트라인바에 연결된 셀의 데이터를 읽을 경우 비트라인 또는 비트라인바 선택을 위한 1개의 N-MOSFET 및 1개의 P-MOSFET 만이 켜져서 비트라인 또는 비트라인바의 전압이 상기 전압차 증폭을 위한 N-MOSFET의 문턱전압을 넘는 지를 기준으로 전압 차이를 증폭하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 11 | 제 1항에 있어서,상기 DRAM 어레이는 64개의 메모리 행으로 구성된 빅 어레이; 8개의 메모리 행으로 구성된 리틀 어레이; 및상기 빅 어레이와 리틀 어레이를 구분하는 비트라인 스위치;를 포함하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 12 | 제1항에 있어서, 상기 MAC 연산은 입력 데이터와 가중치 데이터의 MAC 연산 결과를 낮은 비트(LSB) 위치부터 높은 비트(MSB) 위치까지 순차적으로 누적하는 열 덧셈 데이터 흐름을 갖는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 13 | 제 12항에 있어서,상기 열 덧셈 데이터 흐름은 아날로그 전압 영역에서의 커패시터 결합 방식 및 신호 약화 방식을 통해 아날로그 열 덧셈 연산을 수행할 수 있는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 14 | 제 1항에 있어서, 상기 MAC 연산은 한 쌍의 연산 라인(CL+ 및 CL-)을 갖는 차동 커패시터 어레이 구조로 각 연산 라인은 전체 커패시터개수 중 1/4의 커패시터가 연결된 CL0+와 CL0-, 전체 커패시터 개수 중 1/4의 커패시터가 연결된 CL1+와 CL1-, 및 전체 커패시터 개수 중 1/2의 커패시터가 연결된 CL2+와 CL2-로 나뉘는 분리형 커패시터 어레이 구조를 갖는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |

| 15 | 제 1항, 제 2항, 또는 제 5항에 있어서, 상기 SIMD 연산은 메모리 어레이 외부의 입력 데이터, 메모리 어레이에서 읽은 데이터, 인접한 연산회로의 출력 데이터 중 두 개의 피연산자 간 반복적인 논리 연산을 조합하여 산술 연산을 수행하는 것을 특징으로 하는 고밀도 연산회로와 저전력 감지 증폭기를 주변회로로 이용한 인메모리 컴퓨팅 가속기. |