| 번호 | 청구항 |

|---|---|

| 1 | 다수의 트리플-모드 메모리셀들을 구비하되, 상기 트리플-모드 메모리셀들 각각은 연산모드, 메모리모드, 및 데이터변환모드 중 어느 하나의 동작모드로 동작하는 전환가능 PIM 어레이; 상기 메모리셀들의 동작모드에 따라, 연산기능을 지원하기 위한 연산제어모듈, 또는 데이터 버퍼링을 위한 버퍼 중 어느 하나로 동작하는 재구성형 메모리 유닛; 및외부 제어에 의해 상기 메모리셀들의 동작모드를 결정하는 메모리컨트롤러를 포함하여,연산기, 메모리, 및 데이터 변환기 중 어느 하나로 전환이 가능한 것을 특징으로 하는 DRAM 메모리. |

| 2 | 제1항에 있어서, 상기 전환가능 PIM 어레이는소정비트의 신호를 부호와 크기로 분리하여 처리하기 위해, 부호를 나타내는 1비트의 상기 메모리셀(일명, ‘부호셀’)과, 크기를 나타내는 소정비트의 상기 메모리셀(일명, ‘크기셀’)들을 포함하는 연산단위로 형성된 연산열들을 다수개 포함하는 메모리셀어레이;상기 메모리셀들의 동작모드를 결정하기 위한 제어신호, 또는 입력데이터를 상기 메모리셀어레이로 전달하는 전역입력드라이버; 및ADC 로직, 및 비트간 병렬덧셈트리를 포함하여 상기 메모리셀어레이의 동작을 제어하고, 외부장치들과의 인터페이스를 담당하는 주변로직을 포함하는 것을 특징으로 하는 DRAM 메모리. |

| 3 | 제2항에 있어서, 상기 부호셀은워드라인 신호에 응답하여 온/오프되며 비트라인의 신호를 상기 부호셀 내로 전달하는 제1 트랜지스터;상기 전역입력드라이버를 통해 입력되는 전역입력신호 쌍 사이에 직렬로 연결된 복수의 트랜지스터에 의해 형성된 제1 인버터; 및상기 제1 인버터의 출력단에 연결된 증폭기를 포함하고,상기 전역입력드라이버를 통해 입력되는 전역입력신호 쌍에 의해, 대응된 크기셀의 동작모드를 결정하기 위한 로컬입력신호를 출력하는 것을 특징으로 하는 DRAM 메모리. |

| 4 | 제3항에 있어서, 상기 크기셀은워드라인 신호에 의해 온/오프되어 비트라인의 신호를 상기 크기셀 내로 전달하는 제2 트랜지스터;전원전압과 상기 로컬입력신호 사이에 직렬로 연결된 복수의 트랜지스터에 의해 형성된 제2 인버터; 및상기 제2 인버터의 출력단에 연결된 커패시터를 포함하고,상기 제2 인버터는 상기 로컬입력신호에 의해 곱셈기, 축전기, 또는 데이터 변환기 중 어느 하나로 동작하는 것을 특징으로 하는 DRAM 메모리. |

| 5 | 제2항에 있어서, 상기 주변로직은상기 메모리셀에서 발생하는 누설전류가 PIM 연산결과에 영향을 미치는 것을 방지하기 위해, 상기 메모리셀 내부에서 연산에 사용되는 전압의 범위를 접지전압과 미리 설정된 임계전압 범위 이내의 전압으로 제한하는 것을 특징으로 하는 DRAM 메모리. |

| 6 | 제2항에 있어서, 상기 메모리컨트롤러는연산모드로 동작하는 제1 메모리셀들 및 변환기 모드로 동작하는 제2 메모리셀들로 구성된 제1 연산열에서, 상기 제1 메모리셀들을 이용하여 연산기를 구성하고, 상기 제2 메모리셀들과 상위비트-ADC로 계층적 메모리 내 변환기를 구성하되,상기 제1 연산열로 인가되는 워드라인 및 비트라인을 제어하여, 상기 제1 메모리셀들 각각에 디지털 신호를 기록하고,상기 제2 메모리셀들 각각의 출력을 내부 연산라인(Computation Line, CL)에 연결한 후 상기 제1 메모리셀들에서 생성한 연산라인의 연산 값을 축차 비교 방식으로 바꿔가며 디지털 신호를 아날로그 신호로 변환하여,아날로그 전압을 감지하도록 제어하는 것을 특징으로 하는 DRAM 메모리. |

| 7 | 제6항에 있어서, 상기 메모리컨트롤러는외부 변환기의 사용 여부를 결정하기 위한 기준값을 미리 저장하고,상기 입력데이터가 상기 기준값을 초과하지 않는 경우,상기 입력데이터의 상위비트를 상기 외부 변환기에서 변환하고, 메모리 내부의 하위비트-ADC는 입력데이터의 하위비트(Lower Bits)에 대한 변환만을 수행하며,상기 입력데이터가 상기 기준값을 초과하는 경우,상기 외부 변환기의 동작을 건너뛰도록 제어하는 것을 특징으로 하는 DRAM 메모리. |

| 8 | 제1항에 있어서,연산기로 동작시, 데이터플로우를 형성하는 다른 메모리들과의 리프레시 주기를 동일하게 제어하는 리프레시컨트롤러를 더 포함하는 것을 특징으로 하는 DRAM 메모리. |

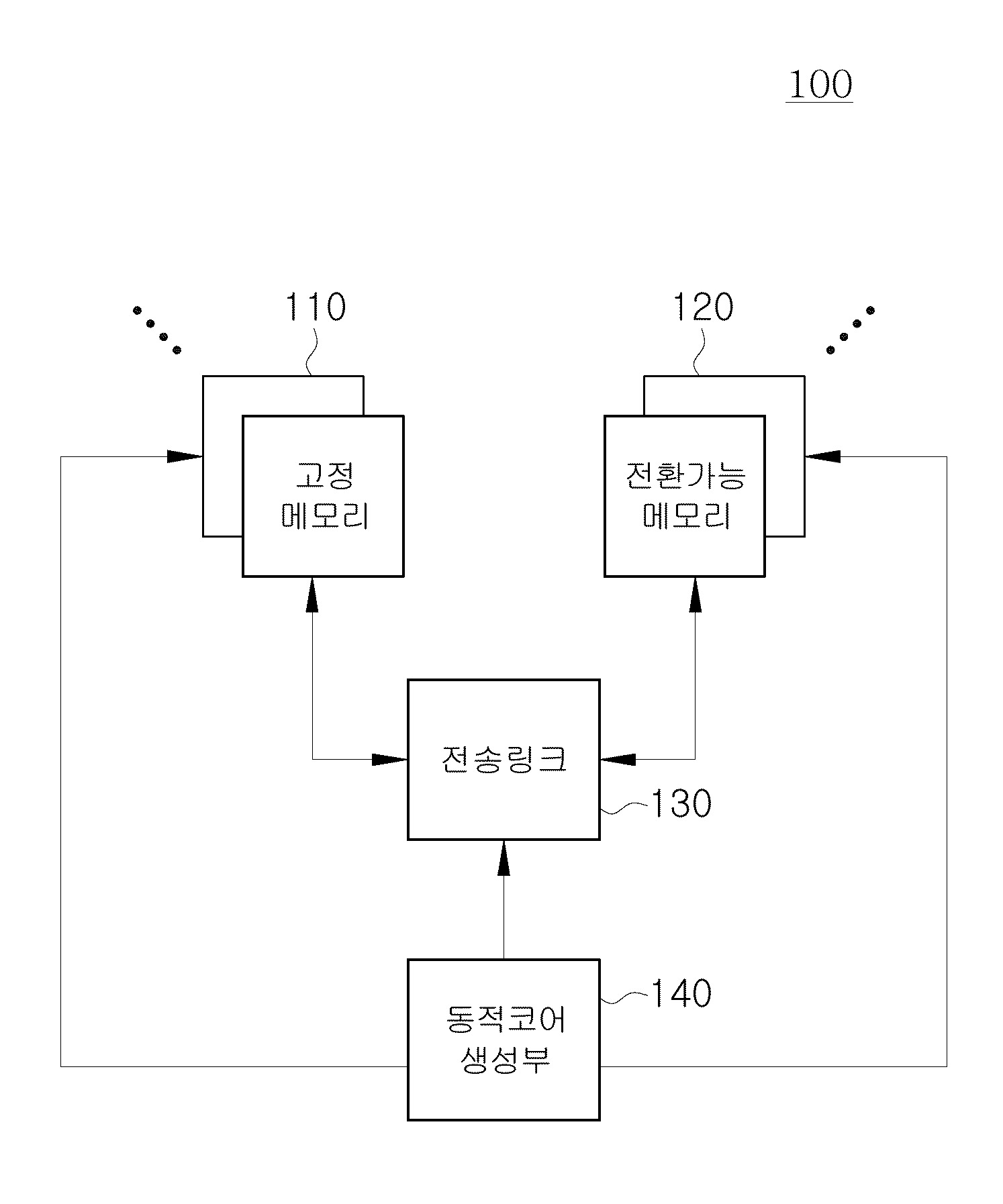

| 9 | 인공지능신경망을 학습시키는 인공지능가속기에 있어서,메모리로만 동작하는 다수의 고정메모리들;연산기, 메모리, 및 데이터 변환기 중 어느 하나로 전환이 가능한 다수의 전환가능메모리들;상기 고정메모리들, 및 상기 전환가능메모리들간의 데이터플로우를 재구성 가능하게 연결하는 다수의 전송링크들; 및상기 인공지능신경망의 구조 및 크기에 의거하여 학습에 참여할 고정메모리들과 전환가능메모리들, 및 학습에 참여할 상기 전환가능메모리들 각각의 동작모드를 결정한 후 그 결과에 의해 상기 데이터플로우를 재구성하여 동적코어를 생성하는 동적코어생성부를 포함하는 것을 특징으로 하는 인공지능가속기. |

| 10 | 제9항에 있어서, 상기 고정메모리는상기 동적코어생성부의 제어에 의해, 다른 고정메모리들 중 적어도 하나, 및 상기 전환가능메모리들 중 적어도 하나와의 데이터플로우를 형성하는 제1 링크스위치부;상기 학습에 필요한 데이터를 저장하기 위한 전역 SRAM; 및상기 전역 SRAM의 입/출력데이터를 버퍼링하는 버퍼를 포함하는 것을 특징으로 하는 인공지능가속기. |

| 11 | 제9항에 있어서, 상기 전환가능메모리는상기 동적코어생성부의 제어에 의해, 다른 전환가능메모리들 중 적어도 하나, 및 상기 고정메모리들 중 적어도 하나와의 데이터플로우를 형성하는 제2 링크스위치부;다수의 트리플-모드 메모리셀들을 구비하되, 상기 트리플-모드 메모리셀들 각각은 연산모드, 메모리모드, 및 데이터변환모드 중 어느 하나의 동작모드로 동작하는 전환가능 PIM 어레이; 상기 메모리셀들의 동작모드에 따라, 연산기능을 지원하기 위한 연산제어모듈, 또는 데이터 버퍼링을 위한 버퍼 중 어느 하나로 동작하는 재구성형 메모리 유닛; 및상기 동적코어생성부의 제어에 의해 상기 메모리셀들의 동작모드를 결정하는 메모리컨트롤러를 포함하는 것을 특징으로 하는 인공지능가속기. |

| 12 | 제11항에 있어서, 상기 전환가능 PIM 어레이는소정비트의 신호를 부호와 크기로 분리하여 처리하기 위해, 부호를 나타내는 1비트의 상기 메모리셀(일명, ‘부호셀’)과, 크기를 나타내는 소정비트의 상기 메모리셀(일명, ‘크기셀’)들을 포함하는 연산단위로 형성된 연산열들을 다수개 포함하는 메모리셀어레이;상기 메모리셀들의 동작모드를 결정하기 위한 제어신호, 또는 입력데이터를 상기 메모리셀어레이로 전달하는 전역입력드라이버; 및ADC 로직, 및 비트간 병렬덧셈트리를 포함하여 상기 메모리셀어레이의 동작을 제어하고, 외부장치들과의 인터페이스를 담당하는 주변로직을 포함하는 것을 특징으로 하는 인공지능가속기. |

| 13 | 제12항에 있어서, 상기 부호셀은워드라인 신호에 응답하여 온/오프되며 비트라인의 신호를 상기 부호셀 내로 전달하는 제1 트랜지스터;상기 전역입력드라이버를 통해 입력되는 전역입력신호 쌍 사이에 직렬로 연결된 복수의 트랜지스터에 의해 형성된 제1 인버터; 및상기 제1 인버터의 출력단에 연결된 증폭기를 포함하고,상기 전역입력드라이버를 통해 입력되는 전역입력신호 쌍에 의해, 대응된 크기셀의 동작모드를 결정하기 위한 로컬입력신호를 출력하는 것을 특징으로 하는 인공지능가속기. |

| 14 | 제13항에 있어서, 상기 크기셀은워드라인 신호에 응답하여 온/오프되어 비트라인의 신호를 상기 크기셀 내로 전달하는 제2 트랜지스터;전원전압과 상기 로컬입력신호 사이에 직렬로 연결된 복수의 트랜지스터에 의해 형성된 제2 인버터; 및상기 제2 인버터의 출력단에 연결된 커패시터를 포함하고,상기 제2 인버터는 상기 로컬입력신호에 의해 곱셈기, 축전기, 또는 데이터 변환기 중 어느 하나로 동작하는 것을 특징으로 하는 인공지능가속기. |

| 15 | 제12항에 있어서, 상기 주변로직은상기 메모리셀에서 발생하는 누설전류가 PIM 연산결과에 영향을 미치는 것을 방지하기 위해, 상기 메모리셀 내부에서 연산에 사용되는 전압의 범위를 접지전압과 미리 설정된 임계전압 범위 이내의 전압으로 제한하는 것을 특징으로 하는 인공지능가속기. |

| 16 | 제12항에 있어서, 상기 메모리컨트롤러는연산모드로 동작하는 제1 메모리셀들 및 변환기 모드로 동작하는 제2 메모리셀들로 구성된 제1 연산열에서, 상기 제1 메모리셀들을 이용하여 연산기를 구성하고, 상기 제2 메모리셀들과 상위비트-ADC로 계층적 메모리 내 변환기를 구성하되,상기 제1 연산열로 인가되는 워드라인 및 비트라인을 제어하여, 상기 제1 메모리셀들 각각에 디지털 신호를 기록하고,상기 제2 메모리셀들 각각의 출력을 내부 연산라인(Computation Line, CL)에 연결한 후 상기 제1 메모리셀들에서 생성한 연산라인의 연산 값을 축차 비교 방식으로 바꿔가며 디지털 신호를 아날로그 신호로 변환하여,아날로그 전압을 감지하도록 제어하는 것을 특징으로 하는 인공지능가속기. |

| 17 | 제16항에 있어서, 상기 메모리컨트롤러는외부 변환기의 사용 여부를 결정하기 위한 기준값을 미리 저장하고,상기 입력데이터가 상기 기준값을 초과하지 않는 경우,상기 입력데이터의 상위비트를 상기 외부 변환기에서 변환하고, 메모리 내부의 하위비트-ADC는 입력데이터의 하위비트(Lower Bits)에 대한 변환만을 수행하며,상기 입력데이터가 상기 기준값을 초과하는 경우,상기 외부 변환기의 동작을 건너뛰도록 제어하는 것을 특징으로 하는 인공지능가속기. |

| 18 | 제11항에 있어서, 상기 전환가능메모리는연산기로 동작시, 데이터플로우를 형성하는 다른 전환가능메모리들과의 리프레시 주기를 동일하게 제어하는 리프레시컨트롤러를 더 포함하는 것을 특징으로 하는 인공지능가속기. |

| 19 | 제9항에 있어서, 상기 동적코어생성부는학습대상인 제1 인공지능신경망의 구조 및 크기에 의거하여 학습에 참여할 전환가능메모리의 수를 결정한 후, 해당 수의 전환가능메모리들을 그룹화하여 동적코어를 생성하는 것을 특징으로 하는 인공지능가속기. |

| 20 | 제19항에 있어서, 상기 동적코어생성부는상기 제1 인공지능신경망의 계층별로 형성된 동적코어의 출력메모리를 다음계층의 입력메모리로 사용하도록 데이터플로우를 재구성하는 것을 특징으로 하는 인공지능가속기. |