| 번호 | 청구항 |

|---|---|

| 1 | 반도체 물질을 포함하는 웨이퍼의 상부에 리세스들을 형성하고; 그리고상기 웨이퍼에 어닐링 공정을 수행하여 상기 웨이퍼에 표면 확산 현상을 발생시킴으로써, 상기 리세스들이 서로 연결되어 캐비티를 형성하는 것을 포함하며,기준 온도(T2)에서 상기 어닐링 공정에 의해 상기 리세스들이 상기 캐비티로 변환되기 위해 소요되는 제2 시간에 대한 실제 온도(T1)에서 상기 어닐링 공정에 의해 상기 리세스들이 상기 캐비티로 변환되기 위해 소요되는 제1 시간의 비율(tratio(T1/T2))은 다음 식 (1)에 의해 계산되며,tratio(T1/T2) = e-a(1-T2/T1) ~ 식 (1) (T1, T2: 절대온도, a = E/kBT2, E: 상기 반도체 물질의 활성화 에너지, kB: 볼츠만 상수)상기 제2 시간에 상기 비율(tratio(T1/T2))을 곱하여 얻은 시간 동안 상기 실제 온도(T1)에서 상기 어닐링 공정이 수행되는 캐비티 웨이퍼 제작 방법. |

| 2 | 제 1 항에 있어서, 상기 반도체 물질의 활성화 에너지가 알려지지 않은 경우,상기 기준 온도(T2) 이외의 다른 온도에서 상기 어닐링 공정을 수행하여 상기 리세스들이 상기 캐비티로 변환되기 위해 소요되는 시간을 측정함으로써, 식 (1)의 a값을 계산하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 3 | 제 1 항에 있어서, 상기 웨이퍼에 상기 어닐링 공정을 수행하기 이전에,상기 리세스들이 형성된 상기 웨이퍼의 상면에 커버를 배치하는 것을 더 포함하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 4 | 제 3 항에 있어서, 상기 커버는 상기 웨이퍼와 동일한 반도체 물질을 포함하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 5 | 제 3 항에 있어서, 상기 커버가 배치되지 않은 상기 웨이퍼의 상면에는 공기 중의 산소가 상기 웨이퍼에 포함된 상기 반도체 물질과 결합하여 기체가 생성되고, 상기 기체가 상기 웨이퍼의 상면으로부터 배출되어 상기 웨이퍼의 상면에 결함이 발생하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 6 | 제 1 항에 있어서, 상기 캐비티를 형성한 이후에,상기 웨이퍼의 상부에 평탄화 공정을 수행하는 것을 더 포함하는 캐비티 웨이퍼 제작 방법. |

| 7 | 제 6 항에 있어서, 상기 평탄화 공정은 화학 기계적 연마(CMP) 공정을 포함하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

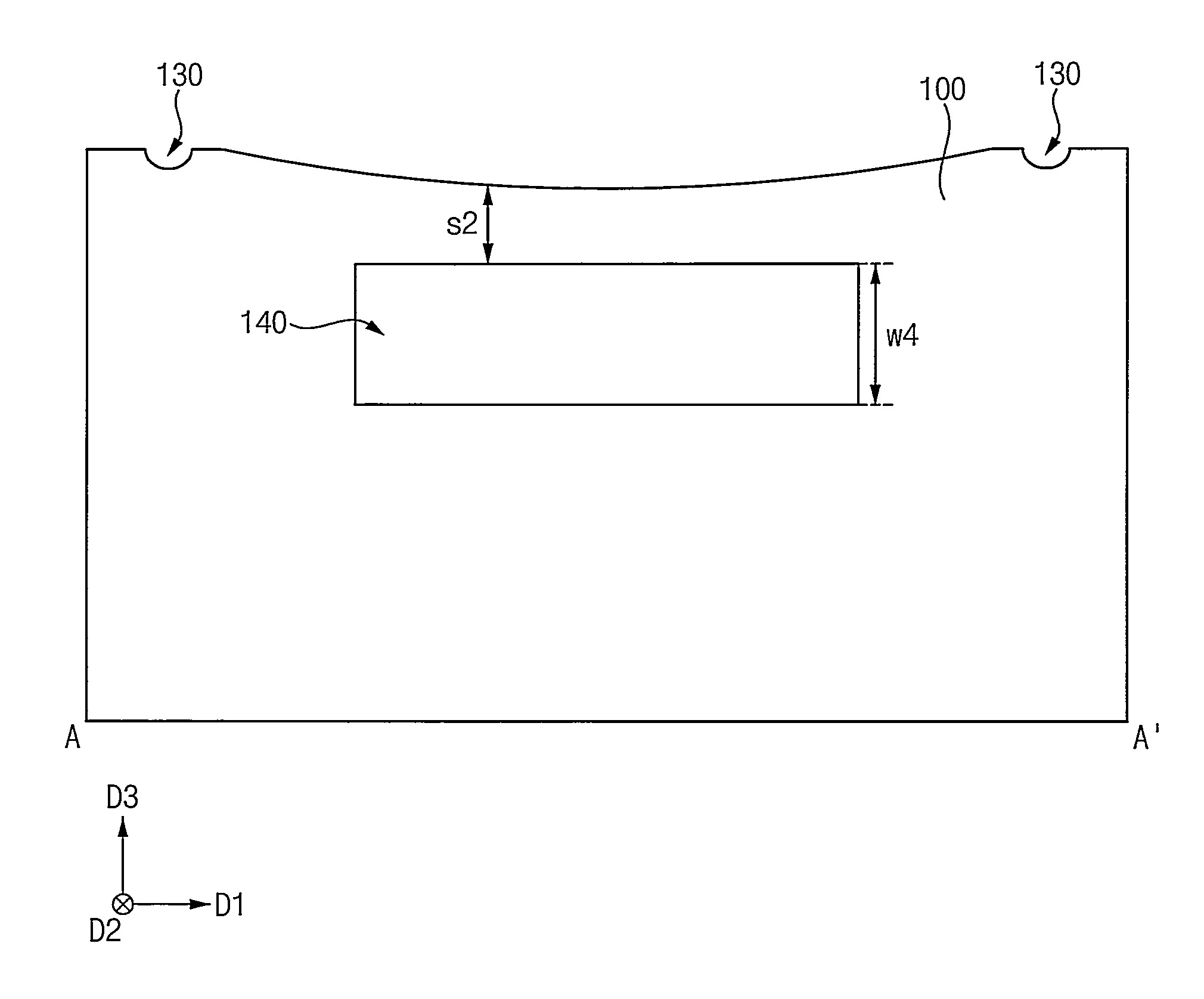

| 8 | 제 6 항에 있어서, 상기 웨이퍼의 상부에 상기 리세스들이 형성된 영역을 둘러싸는 얼라인 키를 형성하는 것을 더 포함하며,상기 평탄화 공정은 상기 얼라인 키에 의해 둘러싸이는 상기 웨이퍼 영역의 상면에 수행되는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 9 | 제 1 항에 있어서, 상기 각 리세스들은 상기 웨이퍼의 상면에 수직한 수직 방향으로 형성된 측벽을 포함하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 10 | 제 1 항에 있어서, 상기 어닐링 공정은 10-6Torr 이하의 고진공 상태에서 수행되는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 11 | 제 1 항에 있어서, 상기 어닐링 공정은 불활성 기체 분위기 하에서 수행되는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 12 | 제 1 항에 있어서, 상기 어닐링 공정은 800도 이상의 온도에서 수행되는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 13 | 반도체 물질을 포함하는 웨이퍼의 상부에 리세스들을 형성하고; 상기 리세스들이 형성된 상기 웨이퍼의 상면에 커버를 배치하고; 상기 웨이퍼에 어닐링 공정을 수행하여 상기 웨이퍼에 표면 확산 현상을 발생시킴으로써, 상기 리세스들이 서로 연결되어 캐비티를 형성하고;그리고상기 웨이퍼의 상부에 평탄화 공정을 수행하는 것을 포함하며,상기 커버가 배치되지 않은 상기 웨이퍼의 상면에는 공기 중의 산소가 상기 웨이퍼에 포함된 상기 반도체 물질과 결합하여 기체가 생성되고, 상기 기체가 상기 웨이퍼의 상면으로부터 배출되어 상기 웨이퍼의 상면에 결함이 발생하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 14 | 제 13 항에 있어서, 상기 커버는 상기 웨이퍼와 동일한 반도체 물질을 포함하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 15 | 삭제 |

| 16 | 제 13 항에 있어서, 상기 평탄화 공정은 화학 기계적 연마(CMP) 공정을 포함하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 17 | 삭제 |

| 18 | 제 13 항에 있어서, 기준 온도(T2)에서 상기 어닐링 공정에 의해 상기 리세스들이 상기 캐비티로 변환되기 위해 소요되는 제2 시간에 대한 실제 온도(T1)에서 상기 어닐링 공정에 의해 상기 리세스들이 상기 캐비티로 변환되기 위해 소요되는 제1 시간의 비율(tratio(T1/T2))은 다음 식 (1)에 의해 계산되며,tratio(T1/T2) = e-a(1-T2/T1) ~ 식 (1) (T1, T2: 절대온도, a = E/kBT2, E: 상기 반도체 물질의 활성화 에너지, kB: 볼츠만 상수)상기 제2 시간에 상기 비율(tratio(T1/T2))을 곱하여 얻은 시간 동안 상기 실제 온도(T1)에서 상기 어닐링 공정이 수행되는 캐비티 웨이퍼 제작 방법. |

| 19 | 제 18 항에 있어서, 상기 반도체 물질의 활성화 에너지가 알려지지 않은 경우,상기 기준 온도(T2) 이외의 다른 온도에서 상기 어닐링 공정을 수행하여 상기 리세스들이 상기 캐비티로 변환되기 위해 소요되는 시간을 측정함으로써, 식 (1)의 a값을 계산하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 20 | 반도체 물질을 포함하는 웨이퍼의 상부에 리세스들을 형성하고; 상기 리세스들이 형성된 상기 웨이퍼의 상면에 커버를 배치하고; 상기 웨이퍼에 어닐링 공정을 수행하여 상기 웨이퍼에 표면 확산 현상을 발생시킴으로써, 상기 리세스들이 서로 연결되어 캐비티를 형성하고;그리고상기 웨이퍼의 상부에 평탄화 공정을 수행하는 것을 포함하며,상기 각 리세스들은 상기 웨이퍼의 상면에 수직한 수직 방향으로 형성된 측벽을 포함하는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |

| 21 | 반도체 물질을 포함하는 웨이퍼의 상부에 리세스들을 형성하고; 상기 리세스들이 형성된 상기 웨이퍼의 상면에 커버를 배치하고; 상기 웨이퍼에 어닐링 공정을 수행하여 상기 웨이퍼에 표면 확산 현상을 발생시킴으로써, 상기 리세스들이 서로 연결되어 캐비티를 형성하고;그리고상기 웨이퍼의 상부에 평탄화 공정을 수행하는 것을 포함하며,상기 웨이퍼의 상부에 상기 리세스들이 형성된 영역을 둘러싸는 얼라인 키를 형성하는 것을 더 포함하고,상기 평탄화 공정은 상기 얼라인 키에 의해 둘러싸이는 상기 웨이퍼 영역의 상면에 수행되는 것을 특징으로 하는 캐비티 웨이퍼 제작 방법. |