| 번호 | 청구항 |

|---|---|

| 13 | 제1항 내지 제4항 및 제6항 내지 제12항 중 어느 한 항에 있어서,상기 복수의 시냅스 소자 각각의 계수 정보는 양의 값 또는 음의 값을 가지는, 뉴런 디바이스. |

| 11 | 제1항에 있어서,상기 출력부는 상기 시분할 다중화 방식에 따른 각 시간 구간에서 출력 신호를 생성하도록 구성되는, 뉴런 디바이스. |

| 12 | 제1항에 있어서,상기 출력부는 상기 가중합이 임계값을 초과하면, 상기 출력 신호를 생성하도록 구성되는, 뉴런 디바이스. |

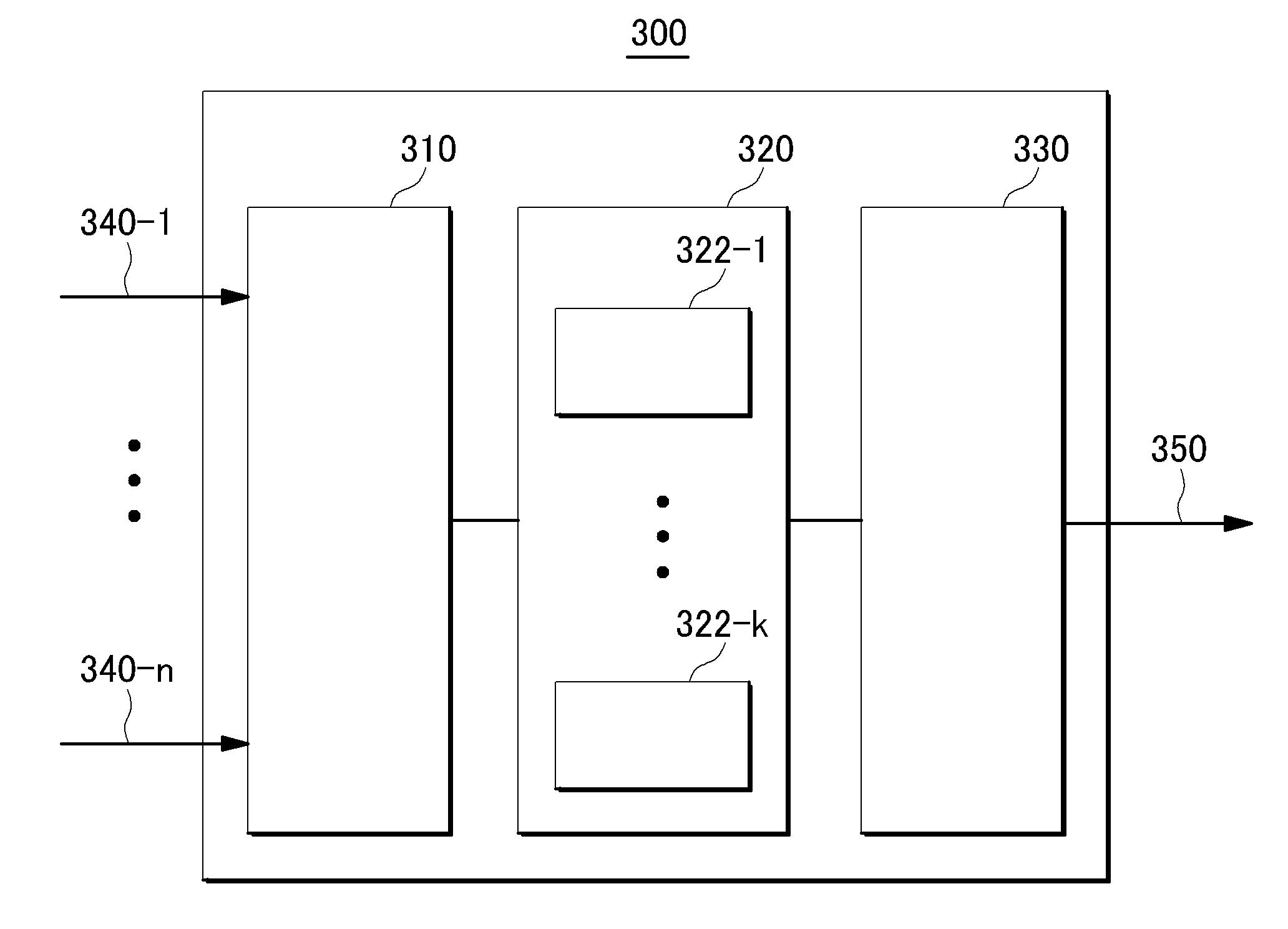

| 1 | 복수의 입력 신호를 수신하도록 구성된 입력부;상기 입력부와 연결되며, 하나 이상의 시냅스 모듈을 포함하는 시냅스부; 및상기 시냅스부와 연결되며, 출력 신호를 생성하도록 구성된 출력부를 포함하고,상기 하나 이상의 시냅스 모듈 각각은 상기 복수의 입력 신호 중 하나에 해당하는 계수 정보를 적용하도록 구성되고,상기 출력부는 상기 하나 이상의 시냅스 모듈에 의해 해당하는 계수 정보가 적용된 하나 이상의 입력 신호의 가중합에 기초하여 상기 출력 신호를 생성하도록 구성되고,상기 시냅스부의 상기 하나 이상의 시냅스 모듈 각각은 그 내부에 복수의 시냅스 소자를 포함하고, 시냅스 모듈의 내부에 포함된 상기 복수의 시냅스 소자 각각은 서로 직렬로 배열되어 연결되며,시냅스 모듈의 내부에 포함된 상기 복수의 시냅스 소자 각각은 해당하는 시냅스 소자 내부에 저장된 특정의 계수 정보를 가지고, 상기 하나 이상의 시냅스 모듈 각각에 의한 해당하는 계수 정보의 적용에 있어서, 상기 복수의 시냅스 소자 각각은 시분할 다중화 방식에 따라 서로 다른 시간 구간에서 동작하도록, 상기 시분할 다중화 방식에 따른 각 시간 구간 마다, 상기 복수의 시냅스 소자 중 동작하는 시냅스 소자는 내부에 저장된 특정의 계수 정보를 대응하는 시냅스 모듈에 의해 적용되는 상기 해당하는 계수 정보로서 상기 복수의 입력 신호 중 대응하는 하나에 적용하도록 구성되는 한편, 상기 복수의 시냅스 소자 중 상기 동작하는 시냅스 소자를 제외한 나머지 시냅스소자는 닫힌 스위치로서 동작하여, 상기 복수의 시냅스 소자 중 상기 나머지 시냅스 소자의 특정의 계수 정보를 시냅스 모듈에 적용하지 않도록 구성되는, 뉴런 디바이스. |

| 2 | 제1항에 있어서,상기 복수의 입력 신호는 펄스 신호인, 뉴런 디바이스. |

| 3 | 제1항에 있어서,상기 복수의 입력 신호는 아날로그 신호인, 뉴런 디바이스. |

| 4 | 제1항에 있어서,상기 복수의 입력 신호는 디지털 신호인, 뉴런 디바이스. |

| 5 | 삭제 |

| 6 | 제1항에 있어서,상기 입력부는 입력 신호를 각각의 시냅스 소자에 직접적으로 전송하도록 구성되는, 뉴런 디바이스. |

| 7 | 제6항에 있어서,상기 입력부는, 상기 시분할 다중화 방식에 따라, 시냅스 소자가 닫힌 스위치로서 동작하기 위한 입력 신호를, 상기 계수 정보를 적용하는 시냅스 소자를 제외한 나머지 시냅스 소자에 전송하도록 구성되는, 뉴런 디바이스. |

| 8 | 제1항에 있어서,상기 입력부는 입력 신호를 각각의 시냅스 모듈에 전송하도록 구성되고,상기 시분할 다중화 방식에 따라, 상기 계수 정보를 적용하는 시냅스 소자들은 계수 정보를 판독 가능하게 하는 판독 신호를 수신하여, 대응하는 시냅스 모듈에 전송된 입력 신호에 계수 정보를 적용하고,상기 계수 정보를 적용하는 시냅스 소자를 제외한 나머지 시냅스 소자는 패스 신호를 수신하여 닫힌 스위치로서 동작하도록 구성되는, 뉴런 디바이스. |

| 9 | 제1항에 있어서,상기 시냅스부의 각각의 시냅스 소자는 상기 시분할 다중화 방식에 따른 각 시간 구간에서 상기 계수 정보를 갱신하도록 구성되는, 뉴런 디바이스. |

| 10 | 제1항에 있어서,상기 복수의 시냅스 소자는 각각 플로팅 게이트 MOSFET로 형성되는, 뉴런 디바이스. |

| 14 | 제1항 내지 제4항 및 제6항 내지 제12항 중 어느 한 항에 있어서,상기 직렬 연결된 시냅스 소자들은 NAND 플래시 구조를 형성하도록 구성되는, 뉴런 디바이스. |

| 15 | 제1항 내지 제4항 및 제6항 내지 제12항 중 어느 한 항에 따른 복수의 뉴런 디바이스; 및상기 복수의 뉴런 디바이스를 상호 연결하도록 구성된 연결부를 포함하는 집적회로. |

| 16 | 제15항에 있어서,상기 연결부는 프로그램 가능한, 집적회로. |

| 17 | 제15항에 있어서,상기 연결부는 상기 복수의 뉴런 디바이스의 상호 연결을 동적으로 변경하도록 구성되는, 집적회로. |